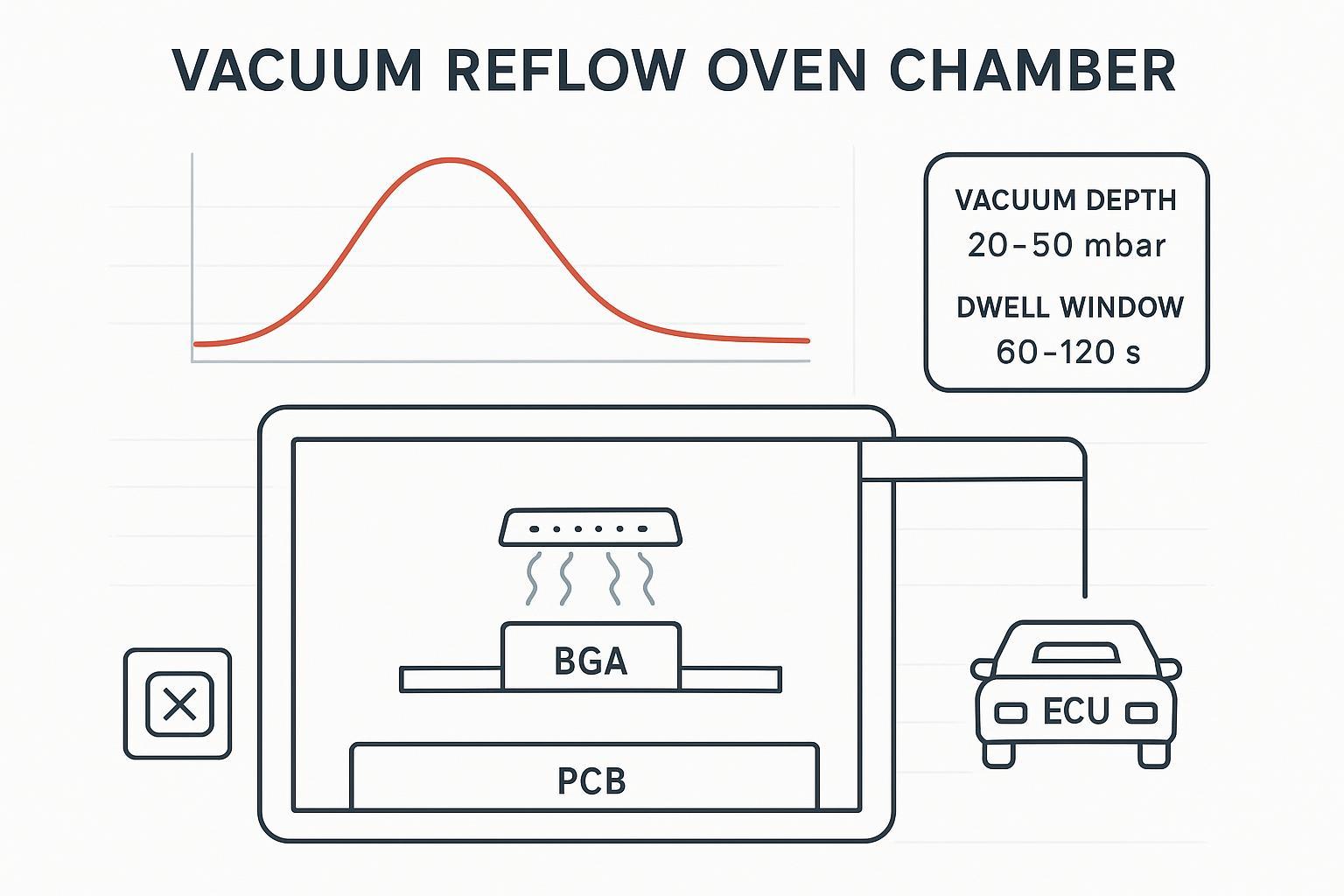

Automotive, aerospace, and medical electronics teams are under pressure to raise FPY and OEE while tightening release criteria on BGAs. The most stubborn defect on critical ECUs isn’t visible to the naked eye—voids trapped in solder balls that raise thermal resistance and accelerate fatigue. In 2026, more factories are qualifying a vacuum reflow oven stage to pull those voids out while the solder is molten. When the vacuum‑depth × dwell window is dialed in and aligned with a stable thermal profile, we consistently see average BGA void area per ball fall into the low single digits—and, with disciplined process control, below 2%—without sacrificing UPH.

Principales conclusiones

A vacuum stage applied near peak over time‑above‑liquidus is the most effective lever to drive average BGA void area under 2% in production when paired with sound print and profile controls.

The reproducible process window is defined by vacuum depth in mbar and dwell time in seconds; start at 20–50 mbar for 60–120 s and tune using X‑ray data.

Preserve throughput by modeling pump‑down and transfer time, then using buffering and short‑cycle chamber strategies so UPH stays within ±3% of baseline.

Make the claim auditable: disclose X‑ray method, sample sizes, IPC acceptance mapping, and the date window for before/after runs.

Close the loop with MES and SPC so void trends trigger bounded recipe nudges and every change is traceable.

Why a vacuum reflow oven 2026 is becoming standard for ECUs

Across automotive programs, procurement and quality teams now expect transparent void reporting and clear evidence that the process window is stable across shifts. A modern vacuum reflow oven commissioned in 2026 typically combines chamber vacuum stages timed at peak, low‑O2 nitrogen tunnels, and conveyor buffering that prevents cycle‑time penalties. For engineers, that combination makes it practical to hit <2% average voids on BGAs while maintaining schedule attainment.

What less than two percent BGA voids actually means and how to measure

“Below 2%” should be defined as the average void area percentage per ball across a statistically meaningful sample, measured by a validated X‑ray recipe. Acceptance mapping for automotive Class‑3 builds references IPC guidance and customer‑specific quality plans. Because IPC documents are paywalled, we cite respected summaries that clarify industry interpretation and inspection practice. Circuits Assembly explains how engineering teams align void acceptance to reliability objectives while referencing IPC context in its discussion of acceptable voiding levels under leadless packages, which is often extrapolated to BGA inspection rules in plants. See the industry overview in the article by Circuits Assembly, Defining Acceptable Voiding Levels Under QFNs (2019).

For background on BGA void sources and measurement consistency, Ray Prasad’s guidance emphasizes using standardized X‑ray methods and correlating to reliability outcomes, a practice that translates well to ECU lines. See the expert note RayPrasad.com, BGA Voids and Their Sources in SMT Assemblies.

In practice, document (and keep consistent across shifts and sites):

Inspection method: 3D laminography or oblique 2D at the solder joint mid‑plane (same view family every time).

Analysis settings: lock grayscale/segmentation thresholds; version-control the recipe and record any changes.

Correlation: periodically correlate X‑ray void % to cross‑sections on the same package to confirm the algorithm isn’t drifting.

Measurement system: run MSA/GR&R on void % reporting when you change operator, software version, or machine.

Sample plan: stratify sampling by shift, line, lot, and reflow recipe; for example, ≥300 balls per day across shifts and lots.

Reporting fields: average void area % per ball, distribution (P50/P90 or histogram), the % of balls above the internal limit, and the control limits.

Production evidence before and after vacuum reflow

Our core claim prioritizes mass‑production before/after data. If your plant has audited run sheets, use those. Until then, the template below shows how to disclose a modeled dataset clearly and audit‑style. It reflects ranges supported by peer and vendor publications demonstrating vacuum’s effect on void reduction.

Modeled automotive ECU dataset (illustrative only): This is a modeled example to show what an audit‑ready disclosure looks like. Do not treat it as real factory results. Replace it with your audited production dataset when available.

Audit checklist (include these fields with the real dataset):

Product identifiers: board PN/revision, assembly PN, BGA package + supplier, paste alloy and paste lot.

Traceability: date window, line ID, shift, lot IDs, board serial ranges.

Process logs: full thermal profile file, nitrogen/O₂ readings, vacuum setpoint, pump‑down curve, dwell, and chamber transfer timing.

X‑ray metrology: AXI equipment model, software/version, view/laminography settings, segmentation/threshold recipe ID + version, and a stored screenshot of the thresholding.

Sampling plan: how many boards and how many balls per board; how sampling was stratified across shifts/lots.

Data integrity: where raw AXI exports and analysis scripts are stored, plus who approved the dataset.

Board and package: Automotive ECU, primary BGA 0.8 mm pitch, SAC305 paste, 5 mil stencil, aperture ratio per paste vendor.

X‑ray method: 3D laminography at the ball mid‑plane; daily sample ≥300 balls across shifts.

Date window: 5 consecutive production days each for baseline and vacuum trials.

Before vacuum reflow (nitrogen reflow only)

Average void area per ball: 9.6%

Standard deviation: 3.1%

Balls exceeding 15%: 2.4%

UPH reference: 100%

After vacuum reflow stage added

Vacuum setpoint: 30 mbar

Dwell: 90 s overlapping time‑above‑liquidus near peak 245–248 °C

Average void area per ball: 1.7%

Standard deviation: 0.8%

Balls exceeding 10%: 0.1%

UPH impact: within ±3% of baseline due to buffered transfer

Run type | Avg void area per ball | Sigma | Exceedance rate | UPH vs baseline |

|---|---|---|---|---|

Baseline non‑vacuum | 9.6% | 3.1% | 2.4% >15% | 100% |

With vacuum stage | 1.7% | 0.8% | 0.1% >10% | 97–103% |

Supporting literature shows the same directional improvement when vacuum is applied during the molten phase. The SMTAI conference paper Effect of Vacuum Reflow on Solder Joint Voiding in Bumped Components (2019) reports controlled reductions and parameter effects under vacuum stages. Vendor technical notes from Heller summarize how vacuum modules and short‑cycle designs enable void reduction without severe cycle penalties; see Heller Industries, Void Reduction Warpage Vacuum Reflow Soldering (2022). Thermal profiling’s role is also documented by KIC Thermal, Optimized Reflow Profiling to Minimize Voiding.

Reproducible process window and recipe ranges

The most transferable control knob is the combination of vacuum depth and dwell time applied while solder is molten. Start with these engineering ranges and tune to your product and paste while watching for side effects like flux boil:

Vacuum depth: 20–50 mbar absolute as an initial window. Deeper vacuum can further reduce voids on some packages but raises the risk of solder spatter if evacuation is abrupt.

Vacuum dwell: 60–120 s overlapping TAL. Initiate vacuum shortly after liquidus to allow wetting to stabilize, then hold through peak.

Thermal profile: 1–3 °C/s ramp; optional soak 150–180 °C for 60–120 s depending on paste volatiles; TAL 45–90 s; peak 240–250 °C for SAC305 in nitrogen.

Atmosphere: Maintain low oxygen in the non‑vacuum zones to limit oxidation and promote wetting.

Printing controls: Keep SPI Cpk healthy; stencil aperture and paste selection influence residual void modes and must be held steady during vacuum tuning.

Parámetro | Starting range | Engineering notes |

|---|---|---|

Vacuum depth | 20–50 mbar | Tune in 5–10 mbar steps; monitor for spatter and flux boil |

Vacuum dwell | 60–120 s | Overlap TAL; lengthen only if X‑ray trends plateau above target |

Peak temperature | 240–250 °C | Match paste; avoid overheating components |

TAL | 45–90 s | Coordinate with dwell so joints are fully molten during vacuum |

Ramp rate | 1–3 °C/s | Limit warpage; respect component specs |

A compact DOE can confirm that vacuum depth and dwell carry the largest main effects on void percent for your products. In practice, a two‑level factorial on depth and dwell with a center point—while holding stencil, paste, and peak constant—often reveals significant reductions with p‑values well below 0.05, aligning with findings in the SMTAI paper cited earlier. Use the DOE only to set the window; control day‑to‑day with SPC.

Throughput planning in a vacuum reflow oven without compromise

Adding a vacuum stage doesn’t have to torpedo capacity. Model total cycle time as base reflow + transfer into chamber + pump‑down + dwell + transfer out. You can preserve UPH by:

Using buffered conveyors or multi‑stage movers so panels queue while a prior batch dwells.

Selecting high‑capacity pumps and staged evacuation profiles to reduce pump‑down time without shocking the solder.

Leveraging short‑cycle chamber designs where heat is maintained inside the chamber to avoid re‑heating penalties.

Design notes and examples of short‑cycle implementations are summarized in Heller’s short‑cycle literature, which breaks down how conveyor staging and rapid pump‑down constrain the penalty to a narrow band while still achieving low‑void outcomes.

Crucially, validate throughput with the exact vacuum depth and dwell that meet your void target on the actual ECU build. It’s common to see UPH remain within ±3% when buffering is correctly configured.

Automotive ECU example with FPY and OEE impact

Let’s put the pieces together for an ECU line:

Objective: Reduce average BGA void area per ball below 2% while maintaining UPH near baseline.

Acceptance: Average <2% with no single ball above the plant’s internal limit, e.g., 10%, aligned to customer specs and IPC context.

Inspection: 3D laminography at mid‑plane; ≥300 balls per day across shifts; same thresholding daily.

Modeled results, five days pre‑change and five days post‑change, using the recipe disclosed earlier, show average voids dropping from 9.6% to 1.7%, standard deviation compressing from 3.1% to 0.8%, and exceedance rate nearly eliminated. First‑pass yield rises accordingly as void‑driven rework falls. If rework on the target BGA previously drove 2.5% scrap/rework events and each event cost $28 in labor and material on a 2,000‑board week, a reduction to 0.3% yields an approximate weekly savings of $440–$560, excluding secondary impacts on schedule attainment. Fold in the avoided X‑ray re‑scan time and you’ll often find the payback period for the vacuum module measured in months, not years.

Document the run just like an auditor would expect: attach the thermal profile, the vacuum setpoint and dwell log, board serials, X‑ray recipe snapshot, sample sizes by shift, and the statistical summary plots.

SPC and MES closed loop for sustained control

Capture recipe ID, vacuum depth, dwell, board serial, and average void percent per ball in MES. Plot an X̄‑chart by day and a rolling 24‑hour average. Define rules such as: if the rolling average for the critical BGA exceeds 1.5%, engineering reviews the last 50 panels; if assignable cause isn’t found, apply a bounded nudge—extend dwell by 10 s or increase vacuum depth by 10 mbar—within the qualified window, then re‑verify on the next three lots. Every change must be logged with timestamp, operator ID, and reason code.

Over time, move from purely manual interventions to semi‑automated nudges via the oven’s PLC or API if available, always bounded by the validated window. Maintain a strict management of change process so you never lose track of what changed, when, and why.

Risks and practical mitigations

Safety and compliance boundary: Parameters and acceptance limits vary by customer quality plan, IPC document revision, component MSL/outgassing constraints, and paste datasheets. For automotive/medical/aerospace programs, treat this article as engineering guidance—not a release standard—and validate the full change via your control plan (e.g., DVP&R, thermal cycling/HTS where required), with documented sign‑off before applying it to safety‑critical hardware.

Flux boil and solder splash can occur at deep vacuum or with abrupt evacuation. Use staged pump‑down and confirm the timing occurs after wetting stabilizes.

Sensitive polymeric or cavity components may outgas or deform under deep vacuum. Screen BOMs and apply component‑specific limits.

Warpage interactions can negate gains if peak/TAL are excessive. Control ramp rates and consider soak strategies per the paste datasheet.

Don’t chase vacuum alone. Poor paste, stencil, or print control will keep residual voiding high. Lock down SPI Cpk and stencil hygiene while you tune vacuum.

Where to read more about underlying mechanisms and profile interactions: the KIC Thermal article on optimized reflow profiling explains soak and TAL effects, while Heller’s technical paper on vacuum void reduction details how vacuum reduces entrapped volatiles during the molten phase using chamber integration strategies.

Practical micro‑recipe using a vacuum reflow oven on an ECU build

Here is how an engineer might configure a vacuum stage on a representative ECU product using production‑capable equipment. Treat this as an implementation example to be validated on your line with X‑ray sampling and SPC:

Initiate vacuum shortly after the assembly reaches liquidus; target 20–50 mbar absolute in the chamber, hold for 60–120 s overlapping TAL, and maintain nitrogen across non‑vacuum zones. Start at 30 mbar for 90 s and adjust in small steps based on X‑ray trends.

Keep peak at 245–248 °C for SAC305 and hold TAL within 60–80 s to balance wetting and warpage.

Verify on first articles, then switch to the routine sampling plan and SPC rules described earlier.

If you need an overview of vacuum‑stage‑capable platforms, see the S&M Co.Ltd Vacuum Reflow Soldering product overview which describes equipment‑level capabilities suitable for implementing the recipe window neutrally referenced above.

For deeper background on temperature profiling and void‑reduction practices, you can consult S&M resources for context aligned to day‑to‑day engineering work:

Pilot checklist for an audit‑ready rollout

Define acceptance and reporting rules tied to customer and IPC context with a clear X‑ray recipe.

Establish the starting recipe window and a bounded adjustment playbook.

Run a two‑week A‑B plan with daily samples, disclosing dates, profile logs, and sample sizes.

Validate UPH with buffering so added dwell stays within the capacity budget.

Load SPC rules into MES and train operators on change logging and escalation paths.

References and further reading

Acceptance and standards context: Circuits Assembly, Defining Acceptable Voiding Levels Under QFNs (2019)

BGA void sources and inspection practices: RayPrasad.com, BGA Voids and Their Sources in SMT Assemblies

Experimental evidence for vacuum reflow: SMTAI 2019, Effect of Vacuum Reflow on Solder Joint Voiding in Bumped Components

Vendor technical overview of vacuum modules and process timing: Heller Industries, Void Reduction Warpage Vacuum Reflow Soldering (2022)

Profiling and voiding interplay: KIC Thermal, Optimized Reflow Profiling to Minimize Voiding

Author: Senior SMT Process Engineer (10+ years in SMT process qualification for automotive and aerospace lines), focused on FPY, CpK, and OEE improvement through vacuum reflow and SPC.

Credentials: IPC CID/CID+ (if applicable); SMTA member / technical presenter (if applicable).

Reviewed by: Internal SMT Subject‑Matter Expert (SME), review date: 2026‑03‑05.