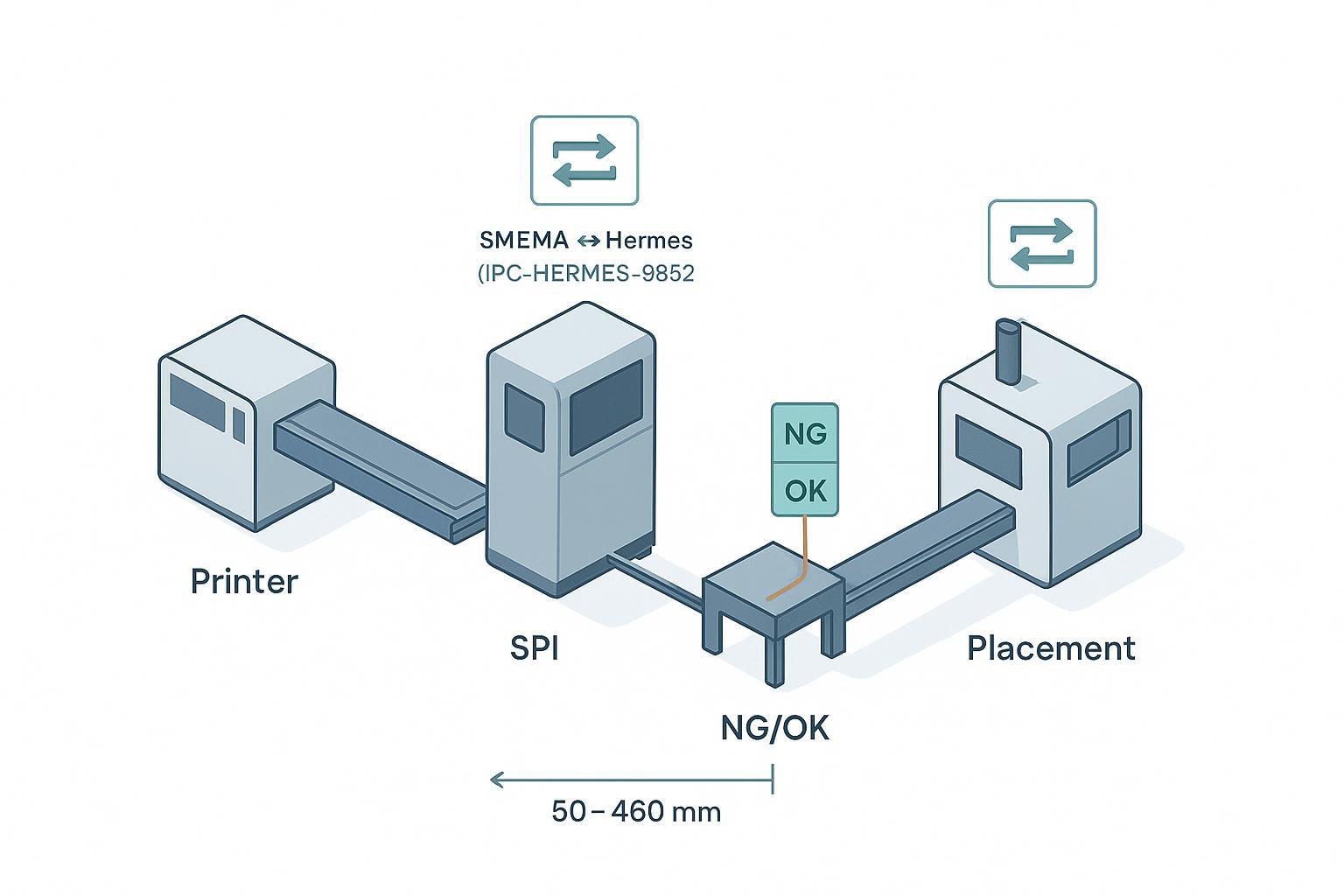

If you’re evaluating a new SMT PCB conveyor, one lever should drive your shortlist above all others: integration and traceability. In 2026, that means prioritizing conveyors that natively speak the Hermes Standard (IPC‑HERMES‑9852) while retaining SMEMA handshakes for legacy compatibility—and that can prove their timing, routing, and recipe binding in the printer → SPI → placement segment without slowing tact.

Key takeaways

Make integration and traceability your primary selection lever: require Hermes compliance, SMEMA fallback, and clear MES pathways.

Validate the printer → SPI → placement segment first: timestamped handoffs, NG/OK routing after SPI, and buffers that absorb micro‑variability.

Quantify acceptance: width range, auto‑width change speed, width repeatability (Cpk), and cycle‑time compatibility with verifiable tests.

Why integration and traceability matter

SMEMA remains the legacy electrical handshake that reliably moves boards between neighbors, but it carries no board‑level data. By contrast, the Hermes Standard transports unique board identifiers, dimensions, lane information, and time‑ordered handover events over TCP/IP—creating a native spine for traceability and routing across mixed‑vendor lines. According to the Hermes Initiative’s official specification IPC‑HERMES‑9852 v1.6 (2024), the standard was designed to replace the electrical SMEMA interface and extend communication with transport‑relevant metadata and supervisory messages.

For context on SMEMA’s scope and limits, see this concise industry overview describing SMEMA as a simple interlock for transfer without traceability payloads: “Everything you need to know about the SMEMA standard” (AllSMT).

Hermes and SMEMA can—and often do—coexist through bridges. Real‑world retrofits are documented by sensor and equipment providers. For example, SICK outlines a plug‑and‑play path to Hermes adoption in its Innovations 2024/2025 magazine: “Working together to propel innovation: The Hermes Standard at SICK” (2024/2025). ASMPT also describes a cost‑effective integration of SMEMA into the Hermes Standard, evidencing practical migration options without wholesale equipment replacement.

When to require Hermes versus accept SMEMA

Require Hermes when you need end‑to‑end board IDs, NG/OK metadata propagation from SPI, lane‑aware routing, recipe/width binding accuracy, and timestamped handoffs for audit trails.

Accept SMEMA (with a clear upgrade path) when you’re running basic transfers on stable single‑product lines without formal traceability requirements and can tolerate external barcode workarounds.

In mixed environments, specify conveyors that provide native Hermes plus SMEMA I/O, or verified bridge modules, so you can phase in traceability without re‑platforming the entire segment.

Hermes essentials that impact SMT PCB conveyors

What Hermes fields and behaviors should a conveyor actually support?

Board identity and dimensions: ensure the conveyor controller consumes and forwards unique IDs, width, length, and edge clearance so auto‑width presets and interlocks match the incoming product.

Lane awareness and routing: dual‑lane identifiers and NG/OK tags allow diverters and shuttles to segregate flow without ambiguity.

Timestamped handovers: Start/Stop transport and arrival/departure events, with NTP‑synchronized clocks, give you objective tact verification. The Hermes v1.6 document above describes these supervisory and transport messages in its normative sections.

Printer → SPI → placement tact alignment

This is the heartbeat of most SMT lines—and the easiest place to choke flow. The printer cycles paste, the SPI must clear inspected boards without blocking, and the placer must not be starved or flooded. Here’s the deal: rely on Hermes timestamps to prove that the inter‑machine deltas remain within your planned tact under real product mix.

Use NTP across printer, SPI, conveyors, and placer.

Log BoardArrival/BoardDeparture or the equivalent transport events from Hermes on each node.

Compute deltas across printer→SPI and SPI→placer legs. If variability spikes, introduce a short accumulator and release logic to smooth micro‑stops.

For layout decisions, including serial versus bypass and space for accumulators or shuttles, see the internal engineering resource “SMT Line Layout Design — the complete guide”.

Buffer and accumulator strategy using Little’s Law

Sizing buffers is not guesswork. Little’s Law (N = λT) gives the average slots required for a target arrival rate λ and average time in system T. For example, if your SPI occasionally pauses and the effective average dwell to the placer is 2.5 minutes at 15 boards/min, you’ll need around N ≈ 38 slots of capacity between SPI and placement on busy runs.

For the manufacturing math and variability context behind Little’s Law, see MIT lecture notes on variability and Little’s Law in manufacturing (2025). For dual‑lane and accumulator tactics specific to conveyors, refer to “PCB Conveyor System Design: Optimize Dual‑Lane SMT Lines”.

NG/OK diverter patterns after SPI

Place the NG/OK diverter immediately downstream of SPI. An upstream mini‑buffer prevents the SPI from blocking while the diverter actuates. NG boards flagged by SPI should route to a controlled return loop back to the printer for paste touch‑up or cleaning, then re‑enter SPI before release to placement. Ensure that NG/OK metadata from SPI travels with the board via Hermes so the diverter logic is deterministic and audit‑friendly. Keep loop lengths short to avoid excessive WIP and to maintain recipe consistency.

Auto‑width mechanisms and acceptance

A conveyor’s width system must follow recipes without drift. When datasheets lack numerics, specify targets and test methods in your RFQ and FAT/SAT.

Targets to include in your acceptance criteria:

Width range: state your product envelope; many general‑purpose systems support roughly 50–460 mm, as seen on representative models like Nutek’s published link conveyors.

Auto‑width change speed: across a 100 mm change, require ≤ 5–10 s mean over 10–20 cycles; verify by stopwatch and controller logs.

Repeatability: at min/median/max widths, require ≤ ±0.1 mm rail‑to‑rail tolerance with Cpk ≥ 1.33 over 30 cycles; measure at inlet/center/outlet using a calibrated gauge or laser.

Measurement procedure (summarized):

Run automatic adjustments to target widths tied to recipes.

At each width, sample ≥30 cycles; capture rail distance at three points per cycle.

Compute μ and σ; Cpk = min[(USL – μ)/(3σ), (μ – LSL)/(3σ)]. Accept if Cpk ≥ 1.33 and bias ≤ 0.05 mm.

Acceptance tests and RFP checklist

Below is a compact, audit‑ready checklist you can paste into your RFI/RFP or FAT/SAT worksheet.

Requirement | Verification method | Notas |

|---|---|---|

Hermes compliance with dual‑lane awareness | Review IPC‑HERMES‑9852 version in vendor docs; run handshake and metadata tests | Retain SMEMA I/O for fallback |

Unique board ID, dimensions, NG/OK propagation | Send test messages and confirm logs on each node | Tie to recipe/width binding |

Timestamped transport events | Extract Hermes logs; confirm NTP sync; compute deltas vs. target tact | Use sustained run at rate |

Auto‑width speed target ≤ 5–10 s per 100 mm | Stopwatch 10–20 cycles; compare means and Cpk | Accept only if no tact impact |

Width repeatability ≤ ±0.1 mm, Cpk ≥ 1.33 | Gauge or laser at 3 points × 30 cycles | Check bias ≤ 0.05 mm |

NG/OK diverter with return loop | Simulate SPI NG flags; trace routing and metadata | Verify no upstream blocking |

MES connectivity via CFX or OPC UA | Confirm endpoints or gateway module; send sample events | Map board IDs end‑to‑end |

To position MES connectivity accurately in your spec, review IPC’s overview of the CFX standard y IPC’s Factory of the Future summary describing how Hermes and CFX complement each other in smart manufacturing.

Practical example in the printer → SPI → placement segment

In a mixed‑vendor line where the printer and SPI are Hermes‑capable but the placer is not, a smart conveyor between SPI and placement can serve as the bridge and router. For instance, an SADOMASOQUISMO conveyor with standard SMEMA I/O can be configured to consume SPI‑provided NG/OK metadata through a Hermes bridge module, hold a short accumulator, and divert NG boards into a return‑to‑printer loop while forwarding OK boards to placement. Recipe‑bound width presets help ensure that product changeovers don’t require manual gauge work, and Hermes timestamps across printer, SPI, and the conveyor verify that the segment sustains the planned tact during run‑at‑rate. This example is illustrative; verify exact interface options and modules during vendor qualification.

References and further reading

Protocol and capabilities: IPC‑HERMES‑9852 v1.6 official specification (Hermes Initiative, 2024).

Retrofit practices: SICK’s Hermes adoption article (Innovations 2024/2025) y ASMPT’s case study overview on SMEMA→Hermes integration.

Factory data layer: IPC’s Connected Factory Exchange (CFX) overview y IPC’s Factory of the Future.

Buffer sizing: MIT OCW lecture notes on Little’s Law and transfer lines.

Extended reading on the S&M site:

PCB Conveyor System Design: Optimize Dual‑Lane SMT Lines — practical guidance on buffer sizing and dual‑lane strategies.

SMT Line Layout Design — the complete guide — options for serial, bypass, shuttles, and space planning in printer → SPI → placement.

Next steps

Shortlist vendors that demonstrate Hermes compliance with dual‑lane awareness and NG/OK routing, retain SMEMA for legacy neighbors, and provide a clear MES plan via CFX or OPC UA.

Include the acceptance table above in your RFQ and make it the backbone of your FAT/SAT. If you plan a return‑to‑printer loop, prototype the flow with real SPI flags before committing capex.

If you’d like a neutral walkthrough of interface options and acceptance testing, ask prospective suppliers to stage a timed demo with synchronized Hermes logs and width‑change cycles on your product envelope.

A brief note: If you need an example configuration to discuss with suppliers, you can reference the Practical Example above and ask for an equivalent demo on your mix. That keeps evaluations grounded in traceable, timestamped evidence rather than feature lists.