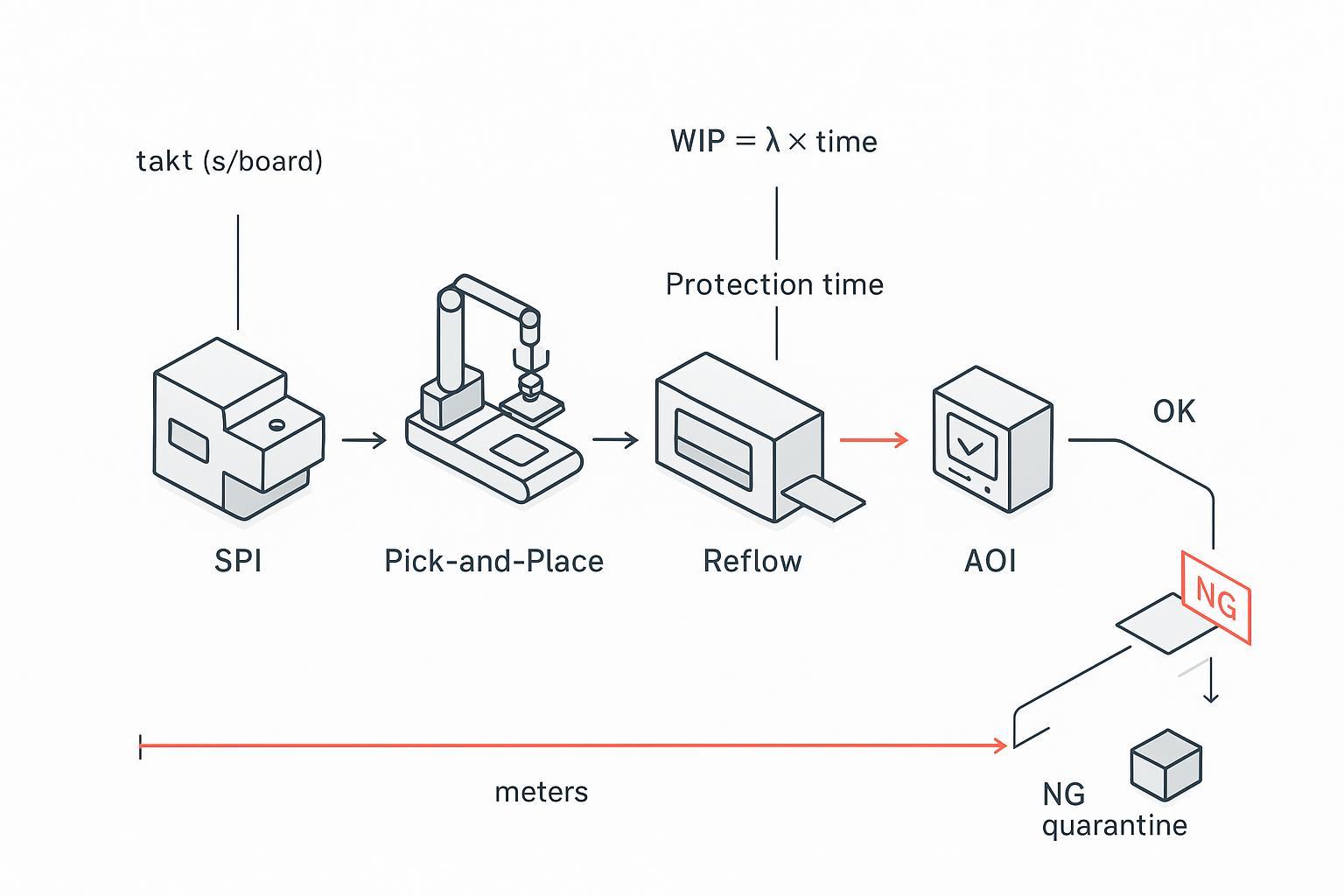

High‑mix builds make takt wobble. SPI and AOI introduce review loops, reflow sets a hard dwell window, and frequent changeovers spike variability. This step‑by‑step guide shows how to plan SMT conveyor capacity—buffers, diverters, and belt speeds—so your line keeps feeding the constraint and protects throughput (UPH) without ballooning WIP.

Key takeaways

Align takt to the composite bottleneck (SPI/AOI review variability plus reflow dwell) and use buffers to absorb shocks, not to hide problems.

Size buffers with Little’s Law: protective WIP ≈ arrival rate × protection time × (1 + safety factor), then tune with SPC.

Convert reflow profile windows to belt speed and effective takt before finalizing upstream buffer lengths.

Keep OK/NG flows separate and interlocked (SMEMA/Hermes) to prevent FIFO breakage and starvation/blocking.

Validate with thermocouples, MES P95 cycle times, and buffer‑penetration KPIs; recalibrate after each changeover.

Step‑by‑step SMT conveyor capacity planning checklist

Before you start changing hardware, ensure the plan follows a repeatable method you can audit later. The following steps implement SMT conveyor capacity planning in a way that aligns takt and buffers to the composite constraint.

Step 0 — Gather the right inputs before you calculate

Pull these from MES/AOI/SPI logs and from your equipment datasheets. You’ll use them in every sizing step. Keep this concise; long shopping lists slow teams down.

Collect: board/panel size and panelization; target UPH per lane and number of lanes; board pitch or spacing; SPI/AOI mean and P95 cycle times, review/recall rate, coefficient of variation (Cv), and notes on program maturity; reflow zone lengths, allowable belt speed range, and validated profile metrics (ramp, soak, TAL, peak, cool); NG rate and re‑inspect policy; quarantine capacity or magazine counts; changeover frequency, first‑article approval time, recipe stabilization time; available accumulation length (m) before AOI and before reflow; bypass options and dual‑lane availability; SMEMA or Hermes handshakes and MES rules for FIFO/block‑starve prevention.

For conveyor fundamentals and typical edge‑clearance assumptions, see the engineering primer in the PCB conveyor system design guide.

Step 1 — Translate UPH to takt and arrival rate

Takt per lane (s/board): Takt_lane = 3600 ÷ UPH_lane

Arrival rate per lane (boards/s): λ_lane = 1 ÷ Takt_lane

If you run dual‑lane, do this per lane. It’s common for one lane to become dominant due to recipe maturity or feeder layout; don’t average away that reality.

Why it matters: Little’s Law links arrival rate to the protective WIP that keeps your constraint fed when inspection reviews spike or a short changeover stalls upstream loaders. For foundations and assumptions behind Little’s Law, see the production‑system overview by the Project Production Institute and classic lecture notes on L = λW from UCSD.

Step 2 — Check reflow as a potential rate limiter (reflow dwell → belt speed → takt)

Reflow sets a physics‑driven lower bound on takt because boards must meet the validated dwell/profile window.

Core relationships (units consistent):

Dwell_time_per_zone (s) ≈ Zone_length (mm) ÷ Belt_speed (mm/s)

Total_profile_time (s) = Σ zone dwells (preheat + optional soak + reflow/TAL + cool)

Reflow‑derived takt (s/board) must be ≥ Total_profile_time, after accounting for board length and minimum spacing.

Use solder paste datasheets to define acceptable windows, then profile with thermocouples before “locking” belt speed. Typical lead‑free guidance (examples): TAL often 45–60 s, ramp ~1–1.5°C/s, and cooling limits specified; confirm with your chosen paste’s PDS such as Indium’s Indium8.9HFRV Pb‑Free PDS és AIM Solder NC512 SAC305 TDS. Practical overviews on reflow sizing and speed/length relations are summarized in the Surface Mount Process reflow guide.

If your effective feed demand pushes belt speed beyond what the profile allows, reflow—not AOI/SPI—becomes the drum. Plan buffers upstream to protect it from starvation.

Step 3 — AOI/SPI variability and AOI buffer sizing with Little’s Law

Inspection takt is not constant. Review loops, sensitivity changes, and first‑article tweaks inflate P95 and drive local WIP surges. Treat inspection as a service‑time distribution rather than a single number. Variability (Cv) and utilization raise queueing delay; by Little’s Law, higher delay at fixed λ implies higher protective WIP. This principle is standard Factory Physics/Kingman (VUT) reasoning covered in operations literature such as the INFORMS WSC paper on variability.

Define a protection time window that covers typical surges—e.g., the delta between P95 and mean inspection time, plus expected changeover disturbances. Then size the AOI buffer:

Buffer_slots_AOI ≈ λ_lane × Protection_time × (1 + safety_factor)

Start safety_factor at 0.2–0.4 for high‑mix. Increase if Cv is high or if changeovers are frequent; decrease after SPC shows shallow buffer penetration.

Keep OK flow FIFO. Route NG immediately off the main lane to avoid contaminating FIFO (see Step 5 on diverters).

Use this section as your go‑to “AOI buffer sizing” reference when you adjust inspection sensitivity or update programs.

Step 4 — Convert slots to linear meters and place buffers where they matter

Once you have slot counts, convert to physical length:

Required_length (m) ≈ Buffer_slots × (Board_length + Gap) ÷ 1000

Where Gap is your minimum conveyor spacing setting (mm). Prioritize accumulation before AOI (absorbs review spikes and first‑article churn), before reflow (protects the drum from upstream takt wobbles), and in NG quarantine (holds false‑call surges without blocking the OK lane). If space is tight, dual‑lane accumulation with a shuttle/merge can pack more protection time per meter. For merge/split patterns, the working principle of a shuttle conveyor explains lane transfers and gating logic.

Step 5 — Configure OK/NG diverters and interlocks to prevent block/starve

Keep OK and NG flows physically separated. NG goes to quarantine or immediate re‑inspect; OK stays FIFO to the next process.

Handshakes: With SMEMA (IPC‑SMEMA‑9851), use Board Available / Machine Ready state logic to avoid pushing into a blocked downstream; Hermes (IPC‑HERMES‑9852) adds board IDs and richer states (StartTransport, StopTransport, TransportFinished) over TCP so your PLC/MES can enforce FIFO with traceability. Basics are outlined in the SMEMA 9851 overview and the Hermes standard brief.

Starvation control: Gate upstream feed when buffer penetration drops below a threshold; reopen once the constraint’s pre‑buffer recovers.

Blocking control: When downstream is full for a grace period, hold transfers and route NG to quarantine rather than stalling the OK lane.

This is where an “OK/NG diverter” strategy pays for itself in stable flow.

Step 6 — Commissioning and verification you can trust

Reflow validation: Thermocouple the worst‑case board and verify ramp, soak (if used), TAL, peak, and cool against your paste PDS (see Step 2 sources). Lock belt speed only after passing.

SPC on inspection: From MES/AOI logs, compute mean, P95, and Cv each shift for SPI and AOI. Track review rate (%). Alert if P95 creeps or Cv spikes.

Buffer KPIs: Monitor buffer‑penetration percentiles at pre‑AOI and pre‑reflow. If penetration routinely exceeds the designed protection time, expand slots or lift the safety_factor; if it barely gets touched, reclaim length.

Handshake logging: Confirm SMEMA/Hermes transitions and FIFO traces. Investigate any bypass events.

Worked example — Dual‑lane line, composite bottleneck, and buffer sizing

Scenario (inputs from Step 0):

Lanes: 2

Target UPH per lane: 350 → Takt_lane = 3600/350 ≈ 10.29 s/board → λ_lane ≈ 0.0972 boards/s

Board length: 150 mm; Gap: 20 mm

AOI mean 7.5 s, P95 14 s; Protection_time = (P95 − mean) = 6.5 s

Changeover frequency: 3 per shift; add 15% extra protection for review surges → safety_factor start at 0.35

Reflow validated profile: Total_profile_time ≈ 70 s; belt speed and spacing yield reflow‑derived takt ≈ 10.5 s/board (slightly slower than target takt)

Constraint check: Reflow takt (10.5 s) is slower than nominal lane takt (10.29 s). Reflow is the drum. Align the line to ≥10.5 s.

AOI buffer sizing per lane: Buffer_slots_AOI ≈ 0.0972 × 6.5 × (1 + 0.35) ≈ 0.0972 × 6.5 × 1.35 ≈ 0.853 → round up to 1 slot.

In practice, 1 slot is too coarse for shock absorption. For high‑mix stability, set a floor of 3–5 slots per lane pre‑AOI even when math yields <2, then tune via SPC.

Physical length per lane for 4 slots: Required_length ≈ 4 × (150 + 20) / 1000 = 0.68 m. For dual‑lane, budget ≈ 1.36 m pre‑AOI.

Pre‑reflow buffer sizing (often needs more time): Suppose SPI/PnP upstream cause 12 s of occasional starvation risk relative to the 10.5 s reflow takt. Use Protection_time = 12 s and safety_factor 0.35: Buffer_slots_reflow ≈ 0.0972 × 12 × 1.35 ≈ 1.57 → round to 2 slots per lane. Length per lane ≈ 2 × (150 + 20) / 1000 = 0.34 m. Dual‑lane ≈ 0.68 m pre‑reflow.

Neutral micro‑example (hardware fit, no performance claims):

A short pre‑AOI accumulation using an S&M inspection conveyor on each lane can provide the 3–5 slots you budgeted while preserving FIFO and a manual hold point for first‑article checks. If NG surges occur after sensitivity tweaks, route them to a small quarantine using an S&M reject conveyor so the OK lane keeps feeding reflow. For oven parameters and process checks, see the SMT reflow process guide.

Troubleshooting and fast recovery

Blocking at AOI exit or reflow exit: Increase downstream accumulation or add controlled‑release logic keyed to MachineReady/Hermes state. If floor space is tight, consider a dual‑lane merge/split with a shuttle.

Starvation before reflow: Raise pre‑reflow slots or throttle upstream feed less aggressively. Verify that AOI NG routing isn’t stealing OK capacity.

False‑call flood after program tweaks: Quarantine NG on a side lane, escalate SPC review, and temporarily relax AOI sensitivity with engineering approval until the program stabilizes.

Profile drift after changeover: Re‑profile with thermocouples; realign belt speed within paste windows before releasing volume.

Handshake or diverter fault: Enable bypass path, alert the operator, and review SMEMA/Hermes logs to isolate the failure.

A simple worksheet you can copy

Below is a compact field map to mirror in a spreadsheet. Units must be consistent.

Field | Example value | Megjegyzések |

|---|---|---|

UPH per lane | 350 | From plan/MES |

Takt per lane (s) | 10.29 | 3600/UPH |

Arrival rate λ (boards/s) | 0.0972 | 1/Takt |

AOI mean/P95 (s) | 7.5 / 14 | From AOI logs |

Protection time (s) | 6.5 | P95 − mean |

Safety factor | 0.35 | Start 0.2–0.4; tune via SPC |

Buffer slots (AOI) | 1 → set 3–5 | Round up; set floor |

Board length + gap (mm) | 170 | Length + spacing |

Length for 4 slots (m) | 0.68 | Slots × pitch / 1000 |

Reflow profile time (s) | 70 | Verified by TC |

Reflow takt (s) | 10.5 | Speed × spacing constraints |

Next steps for SMT conveyor capacity planning

Validate your reflow window and belt speed with thermocouples before line balancing; keep inspection SPC live each shift. This is the backbone of SMT conveyor capacity planning in high‑mix environments.

If you plan to implement dual‑lane buffers, shuttles, or NG diverters, review lane layouts and gating logic with your controls team. For hardware references and dimensions, you can explore S&M resources such as inspection conveyors, reject handling, and reflow process explainers on the company site. Start with the inspection conveyor page linked in the worked example above.

Sources and further reading

Little’s Law in production systems: overview by the Project Production Institute (2024); academic framing in UCSD notes on L = λW.

Variability impact and buffering principles: see the INFORMS WSC variability paper for queueing implications in manufacturing contexts.

Reflow windows and speed/dwell linkage: Indium8.9HFRV Pb‑Free PDS; AIM NC512 SAC305 TDS; overview from the Surface Mount Process reflow guide.

Handshakes and interlocks: SMEMA 9851 basics és Hermes standard intro.