If you run a high‑mix/low‑volume SMT line, the single most important decision for smoother handoffs is how you select and size the link conveyors and buffers between SPI, AOI, and the reflow oven. Get this right and you prevent starvation and blocking, maintain traceability, and pass audits without drama. Miss it and the oven (often your constraint) sees micro‑stops, AOI reviews ripple upstream, and operators fight bottlenecks all shift.

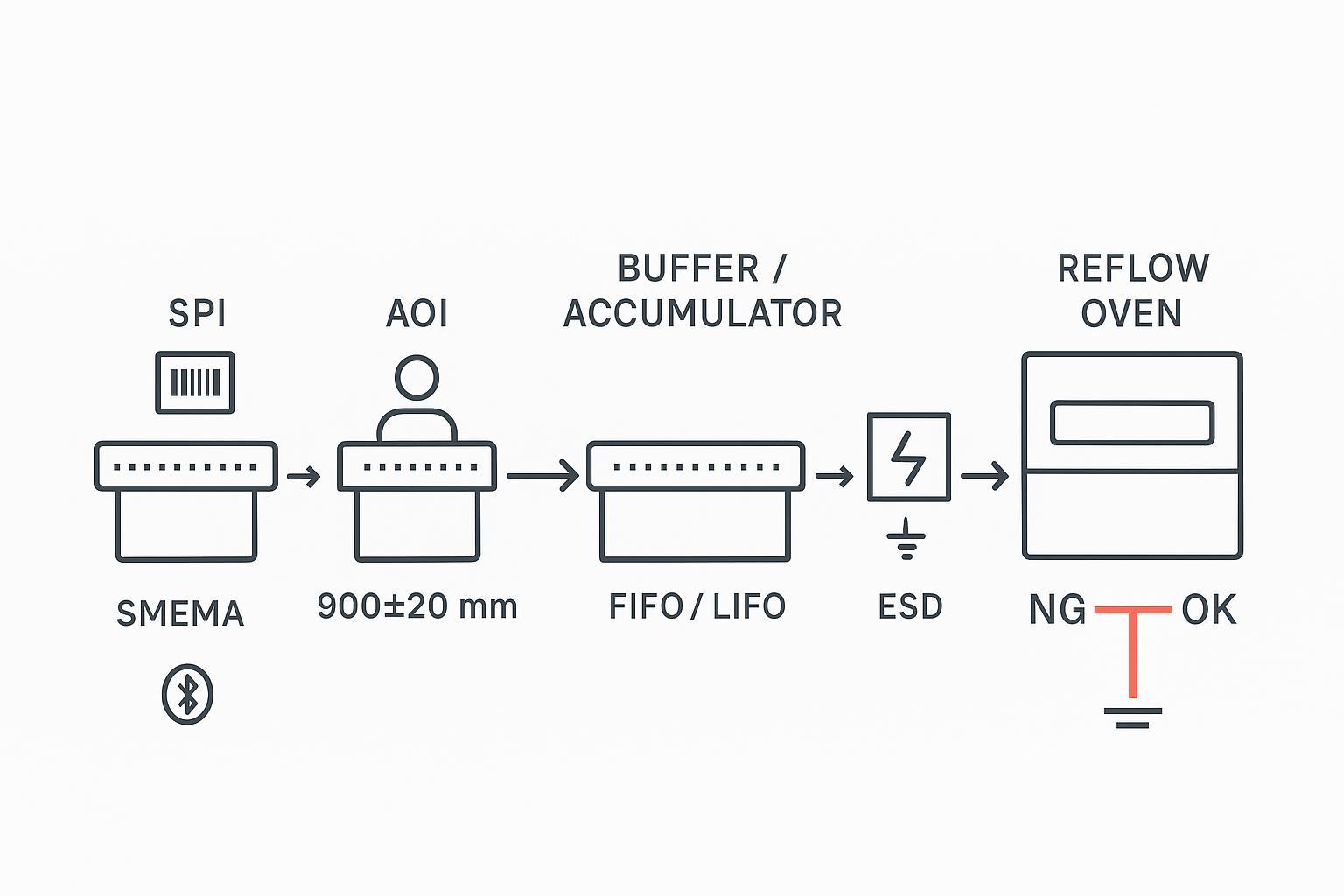

Before we jump in, please confirm or adjust these hard engineering parameters for your line. They drive every recommendation in this guide: board format (single/panel; L×W×T; edge keep‑out, mass, warpage), takt at SPI/AOI/reflow, conveyor height/direction and lanes, interfaces (SMEMA, IPC‑HERMES‑9852, CFX/MES, barcode/ID), buffering policy and capacity (FIFO/LIFO; OK/NG/rework), ESD program scope, and available footprint.

Key takeaways

Optimize for high‑mix changeovers first: prioritize auto width adjustment, recipe‑driven routing, and inspection buffers that decouple AOI reviews from placement and reflow.

Buffer sizing is math, not guesswork: use Little’s Law (slots ≈ arrival_rate × protection_time × (1 + safety_factor)). Start with a 0.2–0.4 safety factor for variability.

Protocol choice shapes routing: SMEMA handles motion handshakes; IPC‑HERMES‑9852 transports BoardId and metadata; CFX/MES carries quality disposition for NG/OK decisions.

Protect the constraint: place an accumulator before reflow and a review buffer after AOI; maintain FIFO on the OK path and isolate NG/rework to keep analytics clean.

ESD and audit readiness matter: qualify materials, bond and ground equipment, and verify per ANSI/ESD S20.20 and IEC 61340 with TR‑53 style logs.

Define your hard engineering parameters

Capture these inputs once; they anchor selection and calculations. Adjust the defaults to match your site standards.

매개변수 | What you must confirm | Typical/assumed range |

|---|---|---|

Board format | Single/panel, L×W×T, edge keep‑out, max mass, allowable warpage | Edge keep‑out 3–5 mm; min thickness 0.6 mm common; validate mass/warpage per fixture |

Takt/throughput | SPI, AOI, and effective oven throughput | Express as boards/min (or s/board) per segment |

Flow geometry | Height and direction; lanes | 900 ± 20 mm height; L→R or R→L; single or dual lane |

Interfaces | SMEMA, IPC‑HERMES‑9852, CFX/MES, barcode/ID | Hermes reduces scanners; CFX links quality to routing |

Buffering | Protection time, capacity, FIFO/LIFO; NG/OK/rework logic | Use Little’s Law; isolate NG, keep OK FIFO |

ESD program | Standards, grounding, verification cadence | ANSI/ESD S20.20; IEC 61340‑5‑1; TR‑53 checks |

Space | Straight lengths, U‑turns, service access | Confirm minimum module lengths and clearances |

If you need a deeper framing for these inputs, see the internal resource on selection scope and acceptance tests in the SMT PCB Conveyor Manufacturer Guide: engineering‑led conveyor selection practices.

PCB link conveyor selection path for high‑mix lines

When boards change frequently, changeover friction—not peak speed—kills OEE. Focus on three levers.

First, make auto width adjustment recipe‑driven. Tie conveyor rail width to product recipes so lanes set themselves during program changeover. Where on‑the‑fly changes are unsafe, ensure width moves complete inside your offline window and verify repeatability and interlocks during FAT/SAT.

Second, choose modules by function and place them to decouple processes. Use link conveyors to bridge SPI↔AOI↔reflow gaps and align heights. Insert inspection conveyors where operators need stop points for barcode confirmation or visual checks. Add accumulators to absorb AOI review spikes and protect reflow from upstream micro‑stops. Introduce diverters or shuttles to split NG/OK or rework bypass, then merge back to a FIFO OK lane.

Third, consider dual‑lane layouts where mix allows. One lane can run the current recipe while the other queues the next, or you can separate NG/OK physically while keeping the primary lane strictly FIFO. Keep diverge/merge geometry compact; confirm diverter actuation times, sensor spacing, and safe stopping distance (a 10–50 mm gap is common depending on speed).

For layout heuristics and step‑by‑step capacity planning examples, this deep dive can help: conveyor capacity planning around SPI/AOI/reflow.

SMT conveyor buffer design with Little’s Law (worked example)

Little’s Law: WIP = λ × W. For protective buffering:

Slots ≈ arrival_rate (boards/s) × protection_time (s) × (1 + safety_factor)

Define arrival rate and protection time. Suppose AOI outputs on average 0.25 boards/s (15 boards/min). You want to protect reflow from AOI review spikes for 2 minutes (120 s). Choose a 0.3 safety factor for high‑mix variability.

Compute slots. Base slots = 0.25 × 120 = 30; with safety factor: 30 × 1.3 = 39 slots.

Convert slots to conveyor length. Assume board length = 150 mm; safe sensor gap = 20 mm → pitch = 170 mm. Length ≈ 39 × 170 mm = 6,630 mm ≈ 6.63 m.

Check sensitivity. If AOI throughput rises to 0.3 boards/s, you need ≈47 slots (about 8.0 m). If protection time can be trimmed to 90 s, ~30 slots (~5.1 m) may suffice. The right answer depends on your SPC of AOI review dwell and rework loops. For more math detail and a slots→meters worksheet, see the internal guide: PCB conveyor system design with Little’s Law.

Protocols and traceability: SMEMA vs. IPC‑HERMES‑9852 (with CFX hooks)

SMEMA excels at simple, robust 24 V I/O handshakes for board ready/transfer but provides no native BoardId or rich context. Traceability and NG/OK routing typically rely on separate scanners or a supervisory system (canonical tables are in IPC‑SMEMA‑9851 via IPC).

Hermes adds Ethernet/TCP with XML messages carrying BoardId, dimensions, lane, timestamps, and transport state. It reduces scanner count and simplifies deterministic routing when paired with downstream intelligence. Public specs cover connectivity (CheckAlive), lifecycle (StartTransport/TransportFinished/StopTransport), readiness (BoardForecast/MachineReady), and notifications. See the Hermes PDFs: The Hermes Standard v1.6 overview 그리고 Best Practices.

Where NG/OK decisions live: Hermes maintains BoardId continuity for physical transfers; quality dispositions typically move via MES/IPC‑CFX using that same BoardId and then command routing elements. For CFX scope, see the IPC‑2591 (CFX) overview materials.

Commissioning checklist (Hermes‑centric). Ensure NTP time sync with line‑wide drift <1 s. Verify CheckAlive and ServiceDescription exchanges and both directions of connections. Exercise the full state chart—StartTransport/StopTransport/TransportFinished—including incomplete handovers and BoardForecast/MachineReady edge cases. Validate configuration change handling (SetConfiguration/GetConfiguration/CurrentConfiguration) and connection resets. Run blocked‑board timeout tests and confirm recovery logic. Retain message traces and confirm BoardId propagation across the segment, including bridges between Hermes and SMEMA equipment.

OK/NG routing and inspection conveyors in practice

Keep the OK stream FIFO and isolate NG/rework. Practically, that means a post‑AOI review buffer with two outcomes: OK continues forward FIFO; NG diverts to a short NG buffer or magazine offload. Avoid letting occasional NG transfers contaminate OK cycle time analytics. For operator ergonomics, inspection conveyors with segmented belts and defined stop points allow barcode confirmation and visual checks without starving upstream. Confirm E‑stop reach, lighting, and esd‑safe worktops.

Neutral, factual example (one reference): A Hermes‑enabled inspection conveyor with auto width adjustment can receive BoardId from upstream, present the board at an operator station, and route NG to a side buffer while letting OK continue FIFO under recipe control. An implementation like this is available from S&M Co.Ltd on its inspection conveyor line; selection still depends on your confirmed parameters and acceptance tests.

ESD and audit readiness between SPI, AOI, and reflow

Your conveyors operate inside the EPA and must fit your ESD control program. Establish and maintain the program to ANSI/ESD S20.20 and IEC 61340‑5‑1/-5‑2. Qualify contact surfaces (belts/rails) as dissipative and bond frames to common point ground; many factories target contact surface resistivity in the 10^6–10^9 Ω/sq range as typical practice—verify locally using ANSI/ESD STM11.11/11.13 and resistance‑to‑ground tests. Keep bonding impedance low; ESDA guidance commonly targets ≤1 Ω from common point ground to AC ground in bonding schemes (confirm per site). Where insulators are unavoidable, deploy ionizers and monitor with field or charged‑plate meters. Use TR‑53‑style compliance logs with daily/weekly/monthly frequencies based on risk. Helpful references include the ANSI/ESD S20.20‑2021 overview and ESDA’s Principles of ESD Control.

Acceptance tests you should run before handover

Treat commissioning as a formal acceptance process. Mechanically, check installation height and alignment against your line standard (~900 ± 20 mm), verify parallelism and datum, and prove buffer/diverter logic under realistic takt. For SMEMA segments, confirm 24 VDC opto‑isolated MR/BA handshakes, timing windows, and any inhibit/fault lines. Validate recovery after E‑stop and power loss.

For Hermes and mixed‑protocol segments, verify NTP synchronization, CheckAlive operation, and accurate ServiceDescription (lane/interface/version/features). Exercise normal and error lifecycles—including incomplete transfers and BoardForecast/MachineReady transitions. Prove Hermes↔SMEMA bridges under blocked/timeout conditions, capture traces, and keep them as part of the SAT record.

Finally, close ESD verification: retain qualification records for belts/rails and frames, resistance‑to‑ground results under worst‑RH, periodic verification schedules, and operator training logs.

Case snapshots and next steps

Case A — High‑mix contract manufacturer. Frequent recipe swaps caused AOI review spikes and starved the oven 7–10 times per shift. Adding a 6.6 m pre‑reflow accumulator (≈39 slots at 0.25 boards/s for 120 s protection with 0.3 safety) and routing NG via MES to a side buffer cut starvation events by ~80%, lifting OEE by about four percentage points while FPY stayed stable.

Case B — Regulated medical line. Audit findings on traceability and ESD logs, plus SMEMA‑only links that made NG routing manual. Introducing Hermes bridges at SPI→AOI and AOI→reflow with a single line‑head scanner, forwarding dispositions over CFX, and adding an inspection conveyor with NG diverter closed nonconformities and reduced manual scans by ~70% without measurable impact on OK takt.

Next steps. If you’re formalizing your specification, start with the requirement list in this guide, then review the engineering‑focused selection primer here: SMT PCB Conveyor Manufacturer Guide. It expands on acceptance tests and procurement checklists. Also, keep the target phrase PCB link conveyor selection in your RFI so vendors respond with the right math and protocol details.

Appendix: quick formulas and checks

Little’s Law (protective buffer): Slots ≈ (boards/s) × (s) × (1 + safety factor). Convert to meters by multiplying slots by (board length + gap).

Hermes commissioning: NTP, CheckAlive, state coverage, configuration resets, blocked tests, traces retained.

ESD logs: include surface resistivity tests, resistance‑to‑ground, ionizer performance, and personnel grounding checks with cadence.

References and standards

Hermes specifications and best practices: v1.6 site PDF 그리고 Best Practices.

IPC‑2591 (CFX) program materials: official overview and TOC.

ESD: ANSI/ESD S20.20 overview 그리고 ESDA fundamentals.