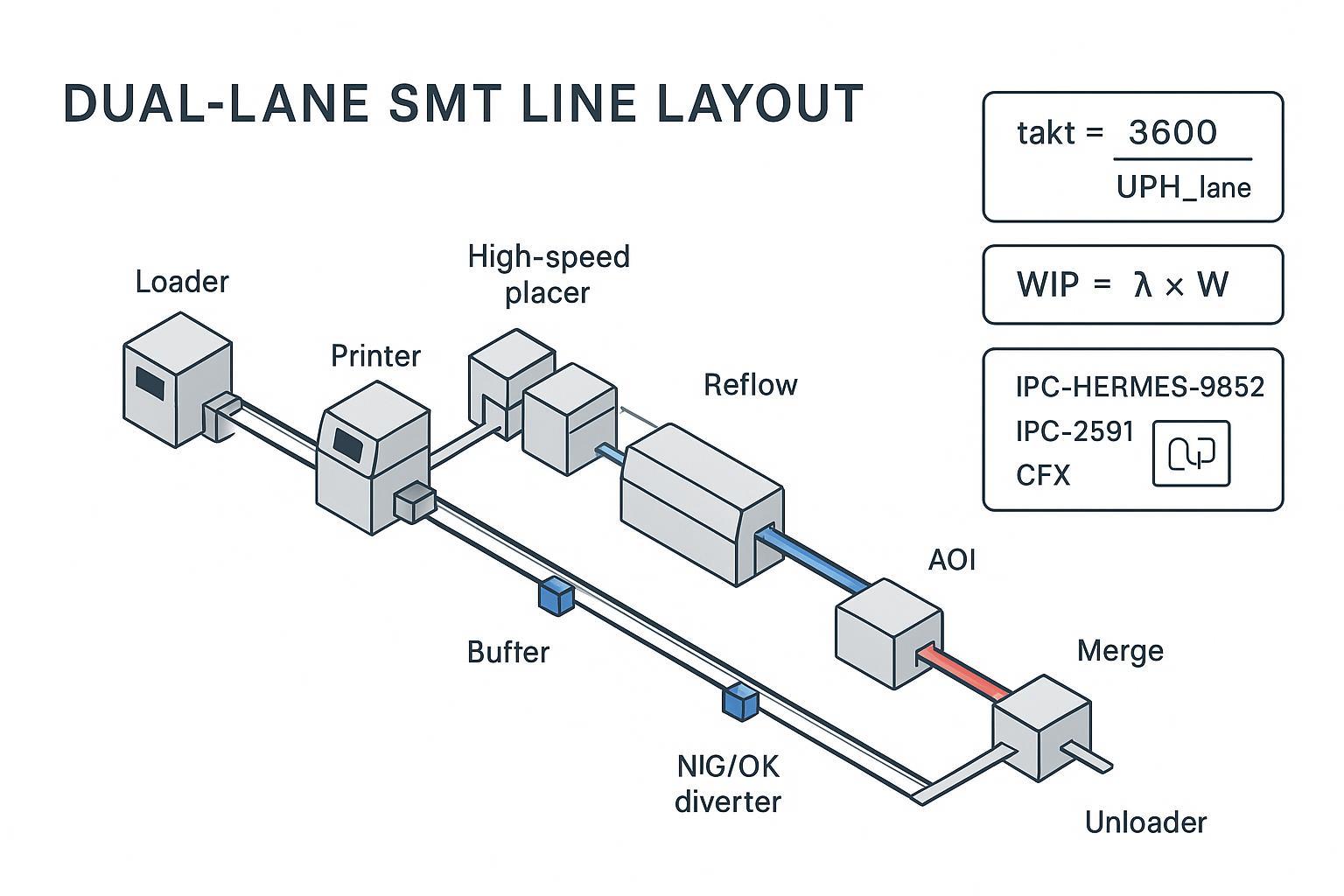

High‑speed consumer electronics lines live or die on conveyor decisions. On dual‑lane SMT layouts, a few millimeters of pitch or seconds of accumulation can be the difference between hitting UPH and babysitting blockages. This ultimate guide shows exactly how to back‑calculate your PCB conveyor system design from target capacity, size buffers with Little’s Law, position NG/OK diverters, and wire in IPC‑HERMES‑9852 plus IPC‑2591 (CFX) for reliable routing and traceability—while keeping SMEMA as a safe fallback. We’ll work through a complete numeric example you can adapt to your factory.

Key takeaways

Start with demand, not hardware: takt per lane (s/board) = 3600 ÷ UPH_lane; UPH_lane = UPH_total ÷ lanes.

Use Little’s Law to size buffers: WIP (boards) = arrival rate λ (boards/s) × waiting time W (s); add 20–40% safety for variability/MTBA.

Place accumulation where it prevents starvation/blocking: post‑loader, printer→placer, placer→reflow, and pre‑AOI.

Hermes handles horizontal board handover with IDs/metadata; CFX carries factory‑level events/traceability; SMEMA remains a fallback. See the official IPC‑HERMES‑9852 v1.6 PDF by The Hermes Standard organization for message flows and lane‑aware fields.

NG/OK routing steals time only when it fires; model its delay as a fractional loss tied to NG% and actuation timing.

For dual‑lane lines, synchronize splitter/merger logic and auto‑width control to lane takt to avoid micro‑stoppages.

What “good” looks like on a dual‑lane high‑speed SMT line

On mature dual‑lane consumer lines, planners target tight, predictable flow rather than peak speed alone. Hallmark outcomes include:

Stable UPH within ±2–3% of plan over a full shift, with Overall Equipment Effectiveness (OEE) > 80% and First Pass Yield (FPY) > 98%.

No chronic starvation at placement and no reflow‑side blocking; visible WIP limits with buffers sized to protect takt, not to hide problems.

Deterministic routing: board IDs and product types are known before each handover; lane merges don’t thrash; NG/OK decisions are executed without ambiguous states.

Changeovers fit into planned windows; width adjustment and recipe selection complete before the next board arrives.

Why does conveyor design dominate these outcomes? Because conveyors and buffers set the cadence between bottleneck machines. A design that respects takt and variability will let your fastest assets actually run; a design that guesses on pitch and accumulation will convert micro‑delays into line‑wide losses. Put plainly, disciplined PCB conveyor system design is a force multiplier for UPH and OEE.

Standards that make routing and traceability work

IPC‑HERMES‑9852 v1.6. The Hermes standard replaces legacy electrical handshakes with a TCP/IP protocol that carries board metadata, including unique identifiers and lane‑aware connections. The v1.6 document formalizes fields such as LaneId and introduces supervisory services for routing and recipe selection. See the official specification in the IPC‑HERMES‑9852 v1.6 PDF by The Hermes Standard organization for scope and message sequences: consult the figures describing ServiceDescription, BoardForecast, and MachineReady exchanges in 2024’s version 1.6.

Reference: The Hermes Standard, IPC‑HERMES‑9852 Version 1.6 (July 2024). Read the official PDF via the Hermes site: https://www.the-hermes-standard.info/wp-content/uploads/IPC-HERMES-9852-Version-1.6-HERMES-SITE.pdf

IPC‑2591 CFX. CFX provides factory‑wide, plug‑and‑play data exchange for real‑time KPIs, material/board genealogy, and quality results. It complements Hermes’ horizontal transport by enabling vertical context in MES/analytics and can inform routing based on AOI/X‑ray outcomes.

Reference: IPC’s overview of Connected Factory Exchange explains roles and complementarity: https://www.ipc.org/about-cfx-global-standard-smart-manufacturing-enablement

SMEMA (IPC‑SMEMA‑9851). SMEMA defines the electrical handshake for board transfer (presence/ready/stop). It carries no board metadata. Keep SMEMA enabled as a fallback for legacy compatibility and fail‑safe transport even when Hermes/CFX are deployed.

Reference: IPC standard overview pages describe SMEMA’s scope and the context for Hermes as its successor.

How they fit together in practice

Hermes moves boards with IDs and product type between adjacent modules and routers/diverters (horizontal).

CFX streams events and quality outcomes to MES (vertical). MES decides NG/OK routing and release strategies; Hermes carries the per‑board route tags to the next node.

SMEMA remains wired so transport is safe even if IP links go down.

Methods and formulas you’ll use

Split target throughput by lanes

UPH_lane = UPH_total ÷ lanes

Takt (s/board) = 3600 ÷ UPH_lane

Yield‑adjusted effective throughput

Effective_UPH = Raw_UPH × (1 − NG%) × (1 − Diverter_Delay_Factor)

Approximate Diverter_Delay_Factor = NG% × (t_divert ÷ takt)

Little’s Law for buffer sizing

WIP (boards) = λ × W, where λ = UPH_lane ÷ 3600 (boards/s) and W is the protection time you want (s). Add 20–40% safety WIP depending on variability (MTBA/MTTR).

Conveyor pitch and speed sanity checks

Pitch ≈ PCB length + gap (typ. 20–80 mm depending on sensor spacing and stop accuracy)

Speed (m/min) ≈ Pitch (m) × (UPH_lane ÷ 60), kept within module specs

These methods are the backbone of practical PCB conveyor system design—consistent math that keeps mechanics and controls aligned with demand.

PCB conveyor system design, step by step — worked dual‑lane example

Scenario

Product: Smartphone mainboard, single PCB (no panel), 150 × 80 mm, 0.8 mm thick, 0.15 kg

Line: Dual‑lane from printer through placement; lanes merge before reflow; post‑reflow AOI with NG/OK diverter and NG loop‑back buffer

Target capacity: UPH_total = 1,200 boards/hour

NG rate at AOI: 2% (sent to repair loop); diverter actuation and decision overhead per NG event: 0.8 s (typical vendor range; validate against the chosen diverter’s datasheet)

Available straight length between modules: 1,000–1,400 mm segments

Interfaces: IPC‑HERMES‑9852 + IPC‑2591 CFX, SMEMA fallback

Takt by lane

UPH_lane = 1,200 ÷ 2 = 600 boards/hour

Takt = 3600 ÷ 600 = 6.0 s/board/lane

Choose pitch and compute conveyor speed

Nominal pitch = PCB length + gap = 150 mm + 30 mm = 180 mm = 0.18 m

Speed needed (per lane) ≈ 0.18 × (600 ÷ 60) = 0.18 × 10 = 1.8 m/min

Sanity: This sits well within common conveyor ranges. For example, an inspection conveyor with 0.5–20 m/min speed capability provides headroom; see the S&M Inspection Conveyor specifications for an example of this speed window: https://www.chuxin-smt.com/products/conveyor-inspection-conveyor/

Size buffers using Little’s Law

Arrival rate λ = 600 ÷ 3600 = 0.1667 boards/s per lane

Protection objectives and W targets

Printer→Placer starvation protection: W = 30 s → WIP = 0.1667 × 30 = 5.0 boards → add 30% safety ⇒ 6.5 ≈ 7 slots per lane

Placer→Reflow blocking protection: W = 90 s → WIP = 0.1667 × 90 = 15.0 → +30% ⇒ 19.5 ≈ 20 slots per lane

Pre‑AOI surge absorption: W = 45 s → WIP = 0.1667 × 45 = 7.5 → +30% ⇒ 9.75 ≈ 10 slots per lane

Account for NG/OK routing penalty

Diverter_Delay_Factor ≈ NG% × (t_divert ÷ takt) = 0.02 × (0.8 ÷ 6.0) = 0.0027 (≈ 0.27%)

Effective_UPH ≈ 1,200 × (1 − 0.02) × (1 − 0.0027) ≈ 1,200 × 0.98 × 0.9973 ≈ 1,173 UPH

Implication: With 2% NG and 0.8 s/event, the routing penalty is small; don’t oversize for this alone—focus on variability and repair loop capacity.

Check physical lengths

A 7‑slot inline accumulator with 180 mm pitch needs ≈ 1,260 mm of effective length (7 × 180 mm), within the 1,000–1,400 mm windows if you use compact buffering (e.g., a short conveyor plus a shuttle or magazine buffer where space is tight).

For 20‑slot protection before reflow, inline length alone would be ≈ 3.6 m per lane; that’s footprint‑heavy. Use a compact accumulator (e.g., vertical buffer or shuttle) sized for 20 boards per lane, or relocate some accumulation pre‑merger where you have space.

Table 1. Inputs and core results (worked example)

Item | Value |

|---|---|

UPH_total | 1,200 boards/h |

Lanes | 2 |

UPH_lane | 600 boards/h |

Takt per lane | 6.0 s/board |

PCB size | 150 × 80 × 0.8 mm |

Pitch | 180 mm |

Conveyor speed target | 1.8 m/min |

NG rate | 2% |

Diverter time (per NG) | 0.8 s |

Effective UPH | ≈ 1,173 boards/h |

Table 2. Buffer sizing by objective (Little’s Law +30% safety)

Location | W target (s) | WIP calc (boards) | Rounded capacity per lane |

|---|---|---|---|

Printer→Placer | 30 | 5.0 | 7 |

Placer→Reflow | 90 | 15.0 | 20 |

Pre‑AOI | 45 | 7.5 | 10 |

Design notes

If floor space is constrained before reflow, consider a shuttle or magazine buffer. A single‑station shuttle can decouple lanes and create compact accumulation; review a single‑station shuttle module’s footprint and compatibility to slot between placer and oven. For a reference design, see a single‑station shuttle conveyor example: https://www.chuxin-smt.com/products/single-station-shuttle-conveyor/

Keep pitch consistent across accumulators and link conveyors so sensors and stop units don’t create micro‑oscillation at merges. This is a subtle but critical aspect of PCB conveyor system design that preserves lane takt.

NG/OK diverters and accumulators: placement, sizing, and timing sensitivity

배치

After reflow AOI, install an NG/OK diverter with a clearly defined NG buffer (repair loop or magazine) and an OK merge back to the unloader. Keep any flip or orientation change off the takt‑critical path unless the product requires it.

Sizing the NG buffer

Expected NG arrival rate λ_NG = (UPH_total × NG%) ÷ 3600. In our example, λ_NG = (1,200 × 0.02) ÷ 3600 ≈ 0.0067 boards/s (≈ 24.0 boards/h).

If the repair station takt is 90 s/board and releases back to AOI or a verification gate, then WIP needed to avoid NG‑side blocking for W = 300 s surge is L = λ_NG × W ≈ 0.0067 × 300 ≈ 2.0 boards. Add 40% safety for repair variability ⇒ ≈ 3 boards of immediate buffer, plus magazine/loop capacity sized for sustained peaks.

Timing sensitivity (illustrative bands; validate with the chosen model’s datasheet)

UPH loss fraction ≈ NG% × (t_divert ÷ takt). With takt = 6.0 s:

t_divert = 0.3 s at 2% NG ⇒ 0.10% loss

t_divert = 0.6 s at 2% NG ⇒ 0.20% loss

t_divert = 1.0 s at 5% NG ⇒ 0.83% loss

Conclusion: Actuation speed matters, but variability and repair flow dominate. Focus on smooth merges and predictable buffer release.

Accumulator choices

Inline accumulators are simple but footprint‑hungry for big W targets. Vertical/multi‑layer buffers compress footprint at the cost of extra mechanics; size by slots, not time alone. For cooling or dwell requirements, pair accumulation with controlled cooling surfaces; see a practical overview of PCB cooling conveyors for considerations like dwell time and heat removal: https://www.chuxin-smt.com/slug-pcb-cooling-conveyors-a-comprehensive-guide-to-smt-quality-and-efficiency/

Micro‑example with a neutral product reference

For inspection or decoupling after the printer, a small adjustable‑speed inspection conveyor (0.5–20 m/min range) can be tuned to the 1.8 m/min target we computed, leaving margin for recovery. An example spec window is documented on the S&M Inspection Conveyor page; this is illustrative only—validate against your chosen vendor and model.

Changeover and auto‑width control for dual lanes

High‑mix isn’t our primary scenario, but even consumer lines face ECOs and SKU rotations. Recipe‑driven auto‑width and early recipe selection prevent dead time.

Width metadata via Hermes. Hermes v1.6 supports conveying product type and lane‑aware connections so downstream modules can prepare before the next board arrives. Use BoardForecast from the upstream splitter; the downstream machine returns MachineReady with the matching ForecastId, then adjusts width before StartTransport.

Recipe binding in MES/CFX. Map ProductTypeId to recipes at the MES. When AOI/X‑ray reports an NG via CFX, the MES tags that board’s route for the diverter using Hermes metadata to carry it to the actuating module.

Practical SOP: Trigger width auto‑adjust as soon as MachineReady is accepted; require a minimum settle time margin equal to 1.2× your lane takt delta to the next arrival.

Further reading: For step‑by‑step considerations on conveyor width adjustment mechanisms and tolerances, see this practical guide on conveyor width control: https://www.chuxin-smt.com/sl/slug-a-comprehensive-guide-to-pcb-conveyor-width-adjustment/

RFP/spec checklist for conveyors and diverters

Use this compact template to request quotes and compare vendors apples‑to‑apples.

Spec field | Requirement in this example | Notes |

|---|---|---|

Speed range (m/min) | 0.5–20 (target setpoint ≈ 1.8) | Verify closed‑loop stability at low speeds |

Pitch control | 180 mm nominal, ±1 mm stop | Sensor spacing and stop accuracy |

PCB size window (L×W×T) | ≥ 150×80×0.8 mm | Check lane center reference |

Lane configuration | Dual‑lane from printer to merge | Splitter/merger compatibility |

Accumulator capacity | 7 / 20 / 10 slots by location per lane | Provide slot pitch and footprint |

Diverter actuation latency | ≤ 0.6 s (typical target) | Verify datasheet and duty cycle |

Interfaces | IPC‑HERMES‑9852 + IPC‑2591 CFX + SMEMA | Include LAN redundancy plan |

Barcode integration | Inline code reader mounts | Lighting and read‑rate targets |

ESD and IP rating | ESD‑safe; IP20+ shop floor | Site‑specific requirements |

PLC/HMI | Recipe and manual jog modes | Maintenance lockouts |

Auto‑width | Recipe‑driven with Hermes metadata | Dual‑lane independent control |

Cooling/dwell (if needed) | Pre‑reflow cooling or dwell spec | Confirm thermal capacity |

Lessons from the field: a short engineering example

A dual‑lane consumer line struggled to exceed 1,050 UPH against a 1,200 UPH plan. Placement never starved on paper, yet the AOI queue oscillated and the reflow entry frequently blocked. A quick study found:

Pitch varied from 170 to 200 mm across ad‑hoc conveyor swaps; at 600 UPH/lane, that created 0.3–0.6 m/min setpoint changes and inconsistent sensor timing.

Pre‑AOI accumulation was only 4 slots per lane—half of the 10 slots Little’s Law justified—so any brief AOI pause caused upstream blocking.

The NG diverter shared a congested merge; actuation occasionally delayed OK flow.

Fix

Standardized pitch to 180 mm across segments and set speed to 1.8 m/min with closed‑loop control.

Added a compact shuttle buffer sized to 10 slots per lane before AOI and relocated the NG diverter to a dedicated bypass with its own short buffer.

Enabled Hermes BoardForecast→MachineReady exchanges at the merge so the downstream unloader could pre‑select recipes and widths.

Outcome

Effective UPH improved to 1,180–1,190 with OEE +6 points. FPY held at 98.3%. Operators reported fewer micro‑stoppages and smoother merges. The lesson: get the math right, then make the mechanics obey the math.

Appendix

Glossary (selected)

Takt: The cadence required to meet demand (seconds per board per lane).

UPH: Units per hour; used here as boards/hour.

Little’s Law: L = λ × W; average WIP equals arrival rate times waiting time.

Hermes: IPC‑HERMES‑9852; TCP/IP protocol for board transfer with metadata.

CFX: IPC‑2591; factory‑wide data exchange standard for events, genealogy, KPIs.

SMEMA: IPC‑SMEMA‑9851; electrical handshake for safe board transfer.

References and further reading

The Hermes Standard’s official IPC‑HERMES‑9852 Version 1.6 PDF includes message flows and lane‑aware fields; see the 2024 specification: https://www.the-hermes-standard.info/wp-content/uploads/IPC-HERMES-9852-Version-1.6-HERMES-SITE.pdf

IPC’s Connected Factory Exchange overview explains CFX’s role and complementarity with Hermes: https://www.ipc.org/about-cfx-global-standard-smart-manufacturing-enablement

A practical explainer of Little’s Law, with examples for WIP and lead time: https://www.isixsigma.com/dictionary/littles-law/

Internal resources (contextual learning)

Example inspection conveyor speed window and sizing context: https://www.chuxin-smt.com/products/conveyor-inspection-conveyor/

Single‑station shuttle module for compact accumulation: https://www.chuxin-smt.com/products/single-station-shuttle-conveyor/

Cooling/dwell considerations for conveyors: https://www.chuxin-smt.com/slug-pcb-cooling-conveyors-a-comprehensive-guide-to-smt-quality-and-efficiency/

Width adjustment mechanisms and tolerances guide: https://www.chuxin-smt.com/sl/slug-a-comprehensive-guide-to-pcb-conveyor-width-adjustment/

About the author and how to validate these numbers

This guide is written from the perspective of an SMT line integration / industrial engineering practitioner with 10+ years working on SMT line layout, dual‑lane transport, buffering, and NG/OK routing across consumer electronics, automotive electronics, and medical device assembly environments.

Validation note: Treat vendor‑specific timing (for example, diverter actuation/decision overhead) as a parameter, not a constant. Before implementing a design, measure your actual lane takt distribution, buffer occupancy behavior, merge micro‑stoppages, and NG routing latency in production (or during a pilot) and then re‑run the calculations with your site data.

Next steps

Adapt the worked example to your board size and UPH target, then run a short pilot: verify speed setpoints, confirm buffer slot counts, and instrument Hermes/CFX events to validate routing timing before full rollout.