Power devices live or die by junction temperature. If the exposed thermal pad under a MOSFET, IGBT, or power module is pocked with voids, heat flow chokes, RθJC climbs, and ΔT at a given dissipation rises. Vacuum reflow addresses the cause—trapped gases and flux volatiles in molten solder—by pulling pressure down during the liquidus window so bubbles expand, escape, and collapse before solidification. The result is a measurable drop in void area and, more importantly, a lower thermal resistance path from junction to case and to ambient. This is where vacuum reflow void reduction power electronics moves the needle from theory to plant-floor results.

This best-practice guide focuses on the power-device bottom thermal pad scenario. We center on a single hard outcome metric—ΔRθJC (or ΔT at fixed power)—and show how to measure it correctly while guarding takt time and nitrogen consumption.

Key takeaways

Lower voids on power-device thermal pads reduce effective thermal resistance (RθJC/RθJA), cutting junction temperature at fixed power.

Apply vacuum during time-above-liquidus at ~10–100 mbar with a controlled dwell and nitrogen backfill; the goal is fewer, smaller voids without disturbing wetting.

Prove value with one primary metric: ΔRθJC (°C/W) or ΔT (°C) at a defined dissipation, measured per JEDEC JESD51-aligned methods and paired with X-ray P50/P95 void statistics.

Expect minimal takt impact when vacuum dwell is short and well-timed; log added seconds and nitrogen flow to defend TCO.

Standardize acceptance with a reproducible micro-test: 15:15 split (convection vs. vacuum), X-ray distribution + cross-section checks, and an RθJC bench test.

Why voids on power thermal pads raise junction temperature

Voids replace high-conductivity solder with low-conductivity gas pockets, shrinking the effective contact area between the device’s exposed pad and the PCB heat spreader. The net effect is higher contact thermal resistance and local hot spots that push junction temperature upward at a given watt load. IPC’s bottom-termination component guidance frames voiding as a design-and-process risk that must be managed, not ignored; see the context in IPC-7093A’s BTC assembly guidance and illustrative voiding figures referenced in its table of contents. For thermal measurement fundamentals and definitions of Rθ terms used by power-package vendors, the Onsemi Solder Reference Manual is a practical primer; it aligns on how RθJC and RθJA are determined in industry practice and how to avoid measurement artifacts.

According to IPC context in the BTC standard overview, managing voiding under large thermal pads is essential for reliable heat transfer; see the guidance in the overview for IPC-7093A: IPC-7093A BTC design and assembly overview.

For thermal resistance terminology and measurement background used by device makers, see Onsemi’s reference manual: Onsemi Solder Reference Manual (thermal basics).

Think of each void as a tiny insulator interrupting the metal-to-metal heat path. Fewer, smaller voids mean a thicker “metal bridge” for heat to flow out—so RθJC drops and ΔT shrinks.

Vacuum reflow void reduction power electronics: do it without killing takt time

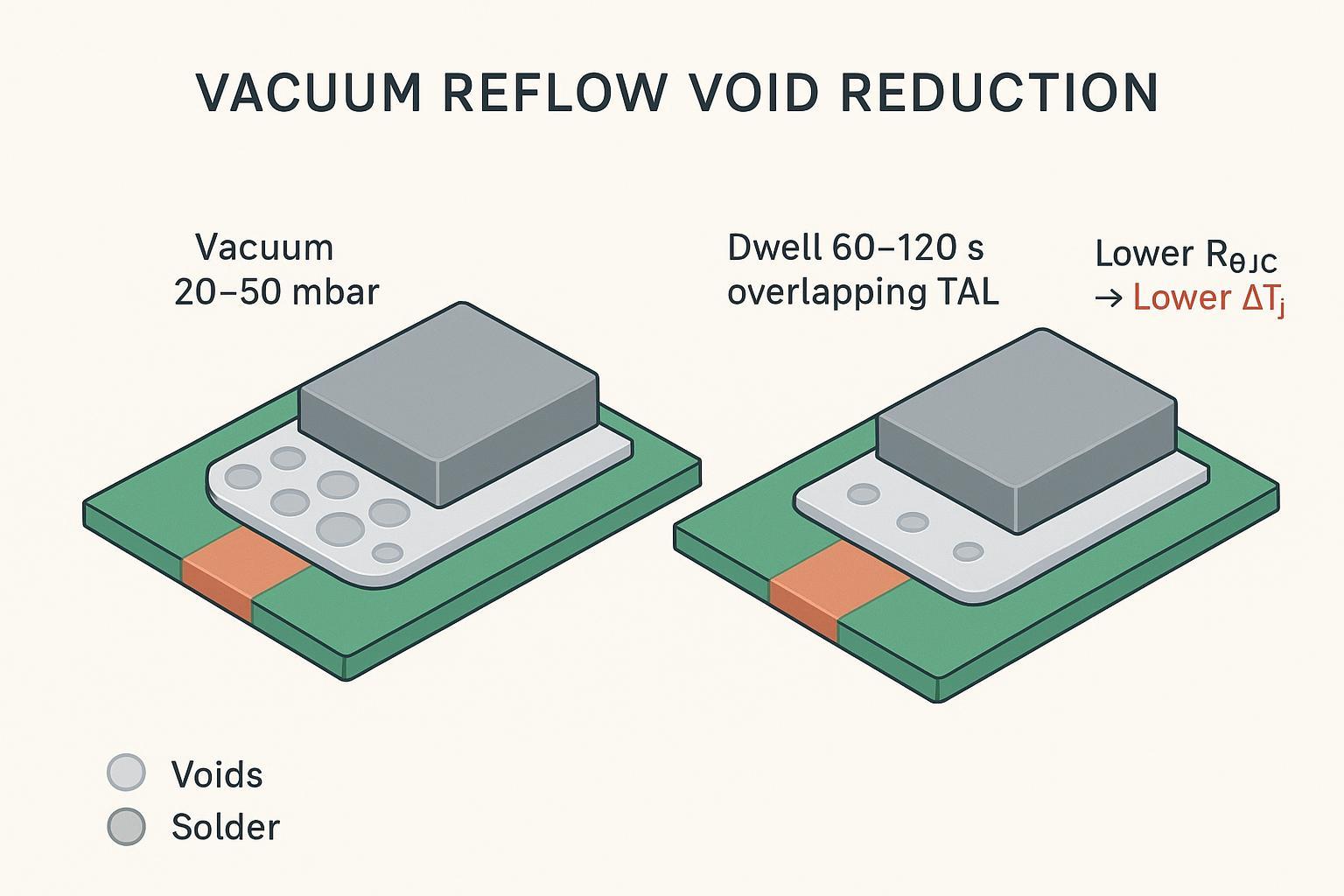

During time-above-liquidus, molten solder can release gases and flux volatiles if pressure is reduced. A vacuum stage lowers absolute pressure, allowing bubbles to expand and rise; when pressure is restored with a clean nitrogen backfill, the joint solidifies with fewer trapped voids. Practical parameter windows published by oven OEMs and process guides converge on similar ranges:

Vacuum depth: roughly 100 down to 10 mbar absolute, engaged immediately after solder melt and held briefly. See the capability context in the Rehm Vision/VisionXP+ Vac brochure: Rehm vacuum reflow capability and timing.

Dwell timing: overlap with the time-above-liquidus window; keep dwell long enough for bubble transport to stabilize but short enough to protect throughput.

Nitrogen management: use controlled backfill to prevent splash or component shift; monitor O2 ppm and flow.

A practical starting window used in production guidance places vacuum depth around 20–50 mbar with a 60–120 s dwell overlapping TAL. For an applied process overview with tuning hints, see the engineering notes here: Vacuum reflow best practices for void reduction.

Takt and operating cost matter. Many modern vacuum ovens are designed to minimize cycle penalties; still, you should record added seconds for the vacuum dwell, pump duty cycles, and nitrogen flow deltas so manufacturing leaders can quantify the impact per 1,000 boards. Here’s the deal: data beats assumptions when you defend ROI.

The one metric that matters: measure ΔRθJC or ΔT correctly

Engineers and auditors will ask, “Did lower voids actually reduce thermal resistance?” Measure it properly and answer with confidence.

Thermal resistance method: Use a JEDEC JESD51-aligned RθJC measurement (e.g., steady-state or transient electrical test) or measure ΔT at a fixed power (e.g., 5 W) and convert to RθJC = ΔT/P. Reference the JEDEC JESD51 series in your method documentation to align with industry norms.

X-ray void quantification: Report distributions, not just means. Include the median (P50) and P95 void-area percentage on the exposed pad and confirm with 2–3 cross-sections.

BTC inspection context: IPC-7095E (BGA guidance) includes practical discussion of void evaluation concepts that map to BTC inspection and sampling approaches. See its overview: IPC-7095E overview for void evaluation concepts.

Pro tip: Pair each thermal measurement set with the corresponding X-ray statistics taken on the same samples. That tightens your causal link between void distribution shifts and ΔRθJC.

Worked example and a micro-test you can reproduce

Below is a compact, reproducible micro-test plan suitable for an engineering pilot. It’s designed to quantify the effect of vacuum reflow on voiding and the resulting ΔRθJC/ΔT, while also logging takt and nitrogen impacts.

Samples: n = 30 identical MOSFET assemblies with exposed thermal pads; split 15 conventional convection vs. 15 vacuum reflow.

Profiles: Conventional follows paste datasheet; Vacuum starts at ~20–50 mbar with a dwell overlapping TAL; controlled nitrogen backfill.

Measurements: X-ray void area % (P50, P95) with 2–3 cross-sections per group; RθJC via a JESD51-aligned method or ΔT at 5 W steady dissipation; record added dwell seconds and N2 flow.

Example before/after summary (illustrative values; replace with your lab data):

Métrica | Conventional Convection | Refluxo em vácuo |

|---|---|---|

Void area % (median, P50) | 9.5% | 2.8% |

Void area % (P95) | 18.0% | 6.0% |

RθJC (°C/W) at 5 W test | 2.10 | 1.85 |

ΔT at 5 W (°C) | 10.5 | 9.25 |

Added dwell seconds | — | +40 s |

N2 flow delta | baseline | +4% |

Interpretation: The illustrative reduction in void distribution (P50 from ~9.5% to ~2.8%) coincides with a drop in RθJC from 2.10 to 1.85 °C/W. At 5 W, that’s a ΔT improvement of ~1.25 °C. It’s not headline-grabbing, but on thermally stressed designs, a few degrees can be the difference between safe headroom and derating. Want a sanity check? Ask whether a 2–3 °C margin would change your thermal throttling limits.

Neutral product example (integration context): On lines using a vacuum-capable oven, engineers typically synchronize vacuum dwell with TAL and log all parameters to MES. For instance, lines built around an S&M vacuum reflow platform can operate in a window like 20–50 mbar with a tightly controlled dwell and nitrogen backfill (capable of ultimate vacuum down to ~0.1–1 mbar and peak temperatures up to 350 °C). A practical overview of such parameterization is shared here: S&M vacuum reflow best practices. Use your own lab’s measurement workflow to confirm ΔRθJC on your device set.

Tuning guide and DoE starting points

Every factory and paste chemistry is different, so treat optimization as a small design of experiments (DoE). Start simple, bound the search, and measure void distributions and RθJC at each step.

Key factors and sensible ranges

Vacuum depth: 10–100 mbar absolute. Deeper vacuum typically reduces voids faster—but watch for splash or component movement at release.

Vacuum dwell: 30–120 s overlapping TAL. Longer dwell aids bubble transport; beyond a point it erodes takt.

Peak temperature and TAL: Follow paste limits; ensure complete melt before vacuum onset.

Nitrogen purity/flow: Maintain low O2 ppm to stabilize wetting; log average flow to quantify TCO.

Paste chemistry/flux volatility: Formulation affects bubble generation and evacuation; keep paste constant while optimizing vacuum.

A practical fractional factorial starter

Two levels each for depth (e.g., 25 vs. 60 mbar) and dwell (45 vs. 90 s), with a center point. Measure P50/P95 void% and RθJC at 5 W. Use main-effects plots to choose the next iteration. If you want to move fast, think of it this way: run the DoE on coupons or small panels first.

Balance vs. takt/N2

For each candidate recipe, record added dwell seconds and nitrogen flow change (Δ%). Reject settings that improve voids marginally but add disproportionate cycle time or gas usage. Your target is the “elbow” where void reduction tapers but takt/N2 remain efficient. This is another practical angle where vacuum reflow void reduction power electronics can deliver wins without operational penalties.

Integration, traceability, and buying checklist

Data integrity makes or breaks adoption decisions. Integrate vacuum reflow into your quality system so void and thermal gains are traceable to recipes and lots.

Integration best practices

MES hooks and recipe versioning: Log vacuum depth, dwell, TAL overlap, peak temperature, O2 ppm, and conveyor speed against serial numbers.

SPC on void distributions: Track P50/P95 void% per lot; set AOI/X-ray thresholds for hold/alert conditions.

Sample cross-sections: Confirm solder wetting and absence of large coalesced voids on a small, periodic cadence.

Buying/specification checklist

Vacuum performance: Ultimate pressure ≤1 mbar; stable control; adequate pump speed; controlled N2 backfill.

Timing control: Programmable dwell and smooth ramp-in/out synchronized with TAL.

Thermal capacity: Peak ≥350 °C; adequate zones; uniformity for thick copper/IMS/DBC; board size and conveyor options.

Flux management: Effective flux recovery/condensation in the vacuum area; documented maintenance intervals.

Throughput/consumption: Quantified cycle-time addition (seconds) and N2/power baselines with vacuum engaged.

Traceability: Native MES connectivity, recipe audit trails, and SPC hooks for void distributions.

For a capability baseline and dimensional/spec context, review this product overview: Vacuum reflow soldering platform (S&M product page).

References and next steps

If your products operate near thermal headroom limits or face tight automotive/medical reliability targets, lowering voids on thermal pads is one of the cleanest levers to pull. Start with a controlled micro-test, measure ΔRθJC or ΔT, and log takt/N2 impacts alongside void distributions. Standards and references to ground your methods include:

Context for BTC voiding and assembly practice: IPC-7093A BTC design and assembly overview

Practical void evaluation concepts transferable to BTCs: IPC-7095E BGA guidance overview

Thermal resistance measurement and terminology background: Onsemi Solder Reference Manual

OEM capability context for vacuum timing and pressure: Rehm Vision/VisionXP+ Vac brochure

Process factor considerations for void minimization: SMTAI presentation on reflow profiles and voiding

Have a line to validate? Request a controlled lab test or schedule a factory demo to profile vacuum dwell versus ΔRθJC on your own device set. For integration and capability context, you can also review S&M’s platform notes: Automotive electronics reliability and traceability context.