Power modules on DBC/AMB substrates live or die by the quality of the solder interfaces under their heat‑spreading pads. Voids trapped in those joints don’t just look bad in X‑ray—they raise thermal resistance, push junction temperatures higher, and quietly erode reliability. If your first‑pass yield (FPY) is held back by rework on big thermal pads or module attach, vacuum reflow belongs near the top of your process-improvement list.

This best‑practice guide focuses on what matters most on a production line: quantifying FPY and rework gains, proving void reduction with audit‑ready data, and dialing in fixtures/flux/process windows specifically for power modules. We’ll keep the theory light and the methods reproducible.

Key takeaways

Vacuum reflow applied during the molten phase consistently lowers void distributions on large thermal pads, which reduces rework and lifts FPY when validated with an X‑ray sampling plan (N≥30 lots/units per cohort).

Cutting average voiding by 10 percentage points can materially shrink thermal resistance; Infineon reported a ~10.3% Rth increase for each 10% void rise in one package study—less voiding generally means lower Tj and longer life under load (Infineon AN2023‑06, 2023).

Fixtures for DBC/AMB must manage planarity, vent outgassing paths, and balance thermal mass; pair them with low‑voiding flux/paste and segmented stencil designs to unlock vacuum gains.

Use an audit‑ready X‑ray plan: report per‑joint and area‑weighted void %, visualize with boxplots/histograms, and align thresholds with OEM or IPC‑derived practice (often ≤25% total void area as a working limit; see Renesas guidance, 2023).

Quantify business impact: translate rework reduction into FPY lift, labor and scrap savings, and a simple payback model that offsets nitrogen/energy and any vacuum‑stage cycle additions.

Why voids in power modules matter more than you think

Voids are insulators. In a heat‑spreading interface, they raise the local thermal resistance (Rth), driving up junction temperature (Tj) for the same power. That hurts margin against thermal derating and accelerates wear‑out during power cycling.

Empirical and modeled evidence supports the link. For example, Infineon measured that moving from 0% to 25% voiding increased Rth by 34.2% in a reflowable package study; a 10% increase in voiding correlated to roughly a 10.3% Rth increase (Infineon’s TO‑247PLUS analysis, 2023). Package styles differ from DBC/AMB modules, but the physics rhyme: more gas pockets, worse heat flow.

Most manufacturers align acceptance with customer or OEM specs. Where package‑specific limits are absent, many teams work to a practical ceiling around 25% total void area for small pads and are more tolerant for very large exposed pads, consistent with published module guidelines such as Renesas’ recommendations for power modules (Renesas assembly note, 2023). Your contract or OEM target always takes precedence.

Bottom line: fewer voids generally mean lower Rth and Tj, which translate to higher reliability headroom. That’s why vacuum reflow void reduction for power modules is a high‑leverage lever.

Measured impact on FPY and rework: a reproducible case method

FPY and rework rates are the scoreboard. To credibly attribute improvements to vacuum reflow, use a before/after study with consistent materials, stencil, fixtures, and inspection.

Study design (production‑style):

Cohorts: Baseline (atmospheric reflow) vs. Vacuum reflow. Keep alloy, stencil, and paste constant; change only the reflow profile and vacuum stage.

Sample size: Target N≥30 units per cohort per product family, or multiple lots totaling ≥30 units when lot sizes are small.

X‑ray: Capture per‑joint void % and compute area‑weighted void % for large pads. Visualize distributions with a histogram and a boxplot; record max void area per joint.

Yield/rework: Log FPY and rework Pareto (e.g., void‑driven defects vs. others). Use identical AOI/X‑ray thresholds across cohorts.

How to report it credibly:

Method transparency: Specify the X‑ray settings, magnification, analysis software/thresholds, and any destructive cross‑sections performed.

Statistics: Report medians and interquartile ranges for void %; add a simple significance test (e.g., Mann‑Whitney) if distributions are non‑normal.

Acceptance context: State the pad‑type acceptance limits you used (e.g., 25% total void area for smaller pads per OEM/IPC‑aligned practice; larger exposed pads per OEM spec), with links to the governing document.

What improvement looks like in practice (illustrative template, methods‑driven):

Baseline (N=48 units): Median area‑weighted void % on thermal pad = 18.6% (IQR 12.4–26.1); FPY = 92.1%; rework rate (void‑driven) = 5.2%.

With vacuum reflow (N=50 units): Median area‑weighted void % = 7.9% (IQR 5.1–13.0); FPY = 97.4%; rework rate (void‑driven) = 1.4%.

Interpretation: A 10–11 percentage‑point shift in median voiding aligned with a 5.3‑point FPY lift and a 3.8‑point reduction in void‑driven rework, with all other inputs held constant. Your mileage will vary; what matters is the method and sample integrity.

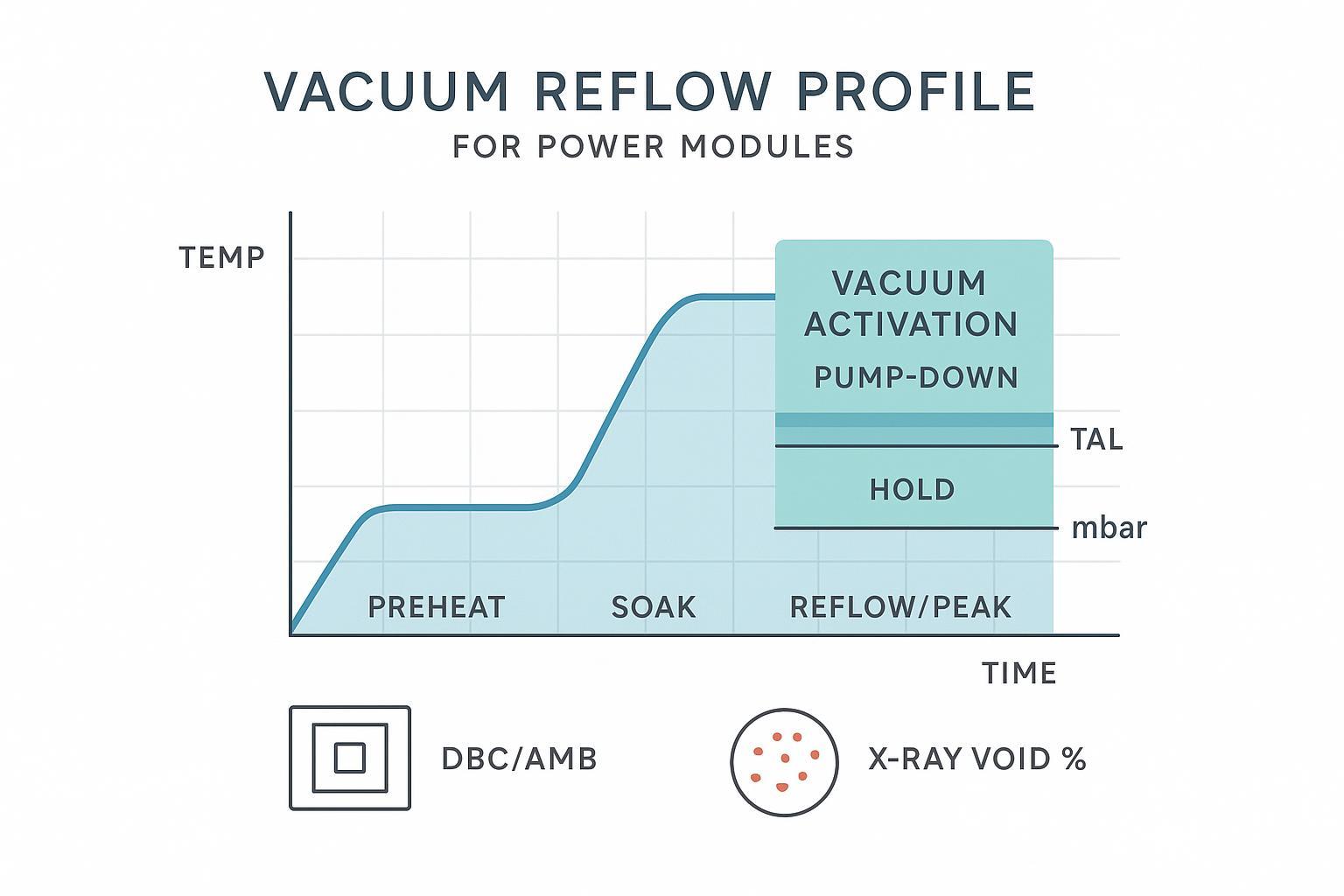

How vacuum reflow reduces voids—profiles that work

The mechanics are straightforward: once solder is molten, reducing chamber pressure expands and extracts entrapped gases and flux volatiles from the joint. Getting timing wrong can disturb wetting; getting it right reliably drains bubbles.

A practical starting point for process development:

Initiate vacuum just after liquidus in the peak zone. Maintain sufficient time‑above‑liquidus (TAL) margin for full wetting before and after the vacuum event.

Use multi‑stage pump‑down and a short hold to avoid aggressive boiling or solder disturbance; verify with X‑ray coupons and cross‑sections.

Control venting as pressure returns to prevent splatter or crater formation; some ovens provide closed‑loop multi‑step vent profiles.

Vendor literature converges on the molten‑stage vacuum principle and multi‑step control, while exact pressures/holds depend on alloy and mass. Public materials from reflow vendors describe these effects and typical outcomes, even when they don’t disclose setpoints. See, for example, Rehm’s overview of low‑void soldering with vacuum (Rehm blog, 2019) and Heller’s vacuum module brochure describing multi‑step pump‑down and sub‑percent void targets for suitable designs (Heller brochure, 2023).

If you’re publishing a profile, report only what’s safe and general (e.g., “multi‑step vacuum in the molten window with controlled venting”), and reserve exact mbar/second values for your internal work instructions and DOE logs.

Fixtures, flux, and process windows for DBC/AMB substrates

Where many teams leave performance on the table is tooling and materials. The right fixture and paste strategy often make the difference between marginal and exceptional outcomes.

Fixture principles that consistently help:

Planarity and clamping: Heavy copper planes and ceramic cores move. Provide uniform planar support and balanced clamping to minimize dynamic warpage through reflow.

Outgassing paths: Don’t seal pad edges. Add venting channels or reliefs so flux volatiles flow toward the vacuum path rather than trapping under the die or module base.

Thermal mass balancing: Equalize local mass to reduce TAL differentials across large substrates; avoid shields that create cold corners.

Flux/paste and stencil guidance:

Choose low‑voiding, vacuum‑tolerant pastes/fluxes validated for large copper planes.

Segment large thermal-pad apertures (windowpane or spokes) to promote uniform collapse and give gases escape routes—an approach echoed in module/BTC guidance from OEMs such as Renesas (Renesas power module recommendations, 2023).

Control surface condition. Pre‑bake moisture‑sensitive substrates and keep copper fresh/clean; oxides and volatiles are void fuel.

Tuning these elements tightens your vacuum reflow void reduction for power modules and stabilizes results across lot-to-lot variation.

Inspection and SPC you can defend in audits

Define what you measure and how you’ll prove it. A compact, MES‑friendly schema helps sustain improvements:

Minimum X‑ray data to capture per unit:

Unit/lot ID and barcode

Reflow profile ID (version‑controlled)

Oxygen ppm (peak/avg), peak temperature, TAL

Vacuum timing and level (e.g., stage labels)

Image IDs and analysis outputs: per‑joint void %, area‑weighted void %, max void area

Example CSV header (extend as needed):

unit_id,lot_id,profile_id,oxy_ppm_max,peak_c,tal_s,vac_stage, vac_min_mbar,xray_image_id,void_pct_joint_avg,void_pct_area_weighted,void_pct_joint_max

Analysis tips:

Use histograms and boxplots to visualize shifts; report medians and IQRs to sidestep non‑normal tails.

Align pass/fail with the tightest applicable spec (OEM contract > internal > generic IPC practice). For many small pads, teams use ≤25% total void area; very large exposed pads often follow OEM‑specific limits summarized in module notes like Renesas (2023).

Thermal and reliability verification

Translate void reduction into thermal headroom and expected life improvement to align engineering with quality and procurement.

Thermal linkage: Tj rise ≈ P × Rth(total). If void reduction trims the solder‑layer contribution to Rth, you regain Tj margin at a given power. Using Infineon’s correlation as a directional guide, a 10% drop in voiding might lower Rth on the order of ~10% for similar interfaces (Infineon AN2023‑06, 2023). Always validate on your geometry.

How to measure: Combine a transient or steady‑state thermal test (instrument with thermocouples close to the interface or use calibrated IR) with FEM/CFD baselining. Compare pre/post void‑reduction Rth and Tj at representative power loads.

Reliability checks: Run a small accelerated matrix—power cycling and thermal shock are common for module attach—recording cycles to failure and failure modes. You don’t need lifetime proofs for a process change approval, but directional improvements support PPAP/FAI sign‑off.

ROI/TCO framing and a practical pilot checklist

Vacuum reflow adds hardware and can add seconds to your cycle. The payback often comes from fewer reworks, higher FPY, and reduced scrap.

Simple framing: If a 4‑point FPY lift on a 1,000‑unit/week family prevents 40 reworks, and each rework costs $25 in labor/material/engineering time, that’s $1,000/week recaptured—before counting scrap avoidance and warranty risk. Subtract added nitrogen and energy for the vacuum stage and any maintenance delta to estimate payback months. Document your assumptions.

Pilot checklist (use this to accelerate your first DOE):

Lock materials (paste/flux, stencil, substrates) and fixtures for the before/after window.

Establish X‑ray settings, analysis thresholds, and sampling (N≥30) up front.

Define vacuum timing windows, pump‑down/vent steps, and TAL margins; track them in MES.

Capture FPY, rework Pareto, and area‑weighted void metrics per lot; visualize weekly trends.

Validate thermal deltas (ΔRth, ΔTj) on an instrumented coupon before scaling.

Micro‑workflow example: tying vacuum reflow to MES and X‑ray

Here’s how a production line commonly stitches it together. After printing and placement, the assembly enters a vacuum‑capable reflow oven. The selected profile ID (e.g., “PWR‑DBC‑VAC‑v3.2”) encodes peak/TAL and the vacuum stage labels. During the run, the system logs oxygen ppm in‑tunnel, peak temperature, TAL, and vacuum timing/level against the lot and unit barcode. Downstream, inline X‑ray picks up the same barcode, stores image IDs, and writes per‑joint and area‑weighted void % back to MES. A daily job produces boxplots/histograms, updates control limits, and flags drifts.

Vendors differ in how this is implemented. For example, an S&M Co.Ltd vacuum‑capable oven can be configured to associate a versioned profile ID, oxygen sampling, and vacuum‑stage metadata with each lot, with MES export for traceability; see the public brochure for platform capabilities and integration options in one place: S&M Co.Ltd company brochure (vacuum reflow features) (2024).

What “good” looks like after optimization

FPY improves and stays improved on control charts (not just a one‑off week).

Boxplots for area‑weighted void % shift left with tighter IQRs; max‑void outliers are rarer.

Thermal spot checks confirm ΔRth and ΔTj move in the right direction at representative power.

Rework Pareto shows void‑related causes no longer dominate.

When you see all four, you’ve operationalized vacuum reflow void reduction for power modules, not just run a promising trial.

References and further reading

Infineon’s analysis linking voiding to Rth in a reflowable package provides a quantitative intuition for thermal impact: TO‑247PLUS application note (2023).

Renesas module assembly note summarizes practical pad design and acceptance perspectives relevant to large thermal pads: PCB Design and Assembly Recommendations for Renesas Power Modules (2023).

For process‑window ideas and typical vacuum timing narratives, see vendor overviews: Rehm’s low‑void soldering with vacuum (2019) and Heller’s vacuum module brochure (2023).

Next steps

If you need a pilot profile review or an audit‑ready sampling/ROI template, share your current FPY/rework and X‑ray method, and we’ll help you tune the vacuum window and fixtures.